资料下载

如何使用FPGA实现语音识别系统的设计资料说明

近年来,语音识别研究大部分集中在算法设计和改进等方面,而随着半导体技术的高速发展,集成电路规模的不断增大与各种研发技术水平的不断提高,新的硬件平台的推出,语音识别实现平台有了更多的选择。语音识别技术在与DSP、FPGA、ASIC等器件为平台的嵌入式系统结合后,逐渐向实用化、小型化方向发展。

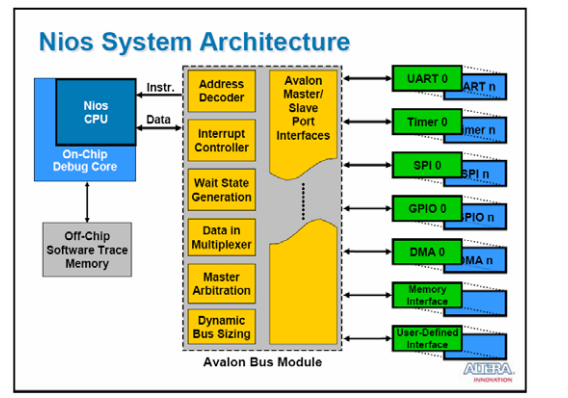

本课题通过对现有各种语音特征参数与孤立词语音识别模型进行研究的基础上,重点探索基于动态时间规整算法的DTW模型在孤立词语音识别领域的应用,并结合基于FPGA的 SOPC系统,在嵌入式平台上实现具有较好精度与速度的孤立词语音识别系统。本系统整体设计基于DE2开发平台,采用基于Nios II的SOPC技术。采用这种解决方案的优点是实现了片上系统,减少了系统的物理体积和总体功耗;同时系统控制核心都在 FPGA内部实现,可以极为方便地更新和升级系统,大大地提高了系统的通用性和可维护性。

此外,由于本系统需要大量的高速数据运算,在设计中作者充分利用了Cyclone II 芯片的丰富的硬件乘法器,实现了语音信号的端点检测模块,FFT快速傅立叶变换模块,DCT离散余弦变换模块等硬件设计模块。为了提高系统的整体性能,作者充分利用了FPGA的高速并行的优势,以及配套开发环境中的Avalon总线自定义硬件外设,使系统处理数字信号的能力大大提高,其性能优于传统的微控制器和普通DSP芯片。本论文主要包含了以下几个方面:

(1)结合ALTERA CYCLONE II芯片的特点,确定了基于FPGA语音识别系统的总体设计,在此基础上进行了系统的软硬件的选择和设计。

(2)自主设计了纯硬件描述语言的驱动电路设计,完成了高速语音采集的工作,并且对存储数据芯片SRAM中的原始语音数据进行提取导入MATLAB平台测试数据的正确性。整个程序测试的方式对系统的模块测试起到重要的作用。

(3)完成高速定点256点的FFT模块的设计,此模块是系统成败的关键,实现高速实时的运算。

(4)结合SOPC的特性,设计了人机友好接口,如LCD显示屏的提示反馈信息等等,以及利用ALTERA提供的一些驱动接口设计完成用户定制的系统。

(5)进行了整体系统测试,系统可以较稳定地实现实时处理的目的,具有一定的市场潜在价值。

嵌入式系统发展趋势为小体积、低功耗、高性能。如今MCU、DSP和FPGA三种处理器在现代嵌入式系统中是三分天下,各自都具有独特的优势但在某方面又存在不足。当前ARM 和51系列单片机为代表的MCU家族在强大的软件系统支持和控制处理微机接口方面占据领先之位;而在大的数据处理方面市场又被DSP抢占;FPGA在高速复杂逻辑处理方面独领风骚,同时其大规模的内部存储容量和内嵌乘法器,高速并行处理能力,在信号处理方面也突出了它的优势。因而三者的结合是未来嵌入式系统发展的趋势。SOPC=MCU+DSP+FPGA,微电子技术发展至今取得了长足的进展,而最终将实现SOC方案。而在整个设计流程中, SOPC技术是一种有效的解决方案。SOPC主要源自全球著名的微电子产商Altera, 其涵义为可编程的片上系统,或者说是基于大规模FPGA的单片系统。之所以如此快速发展,跟目前 CPLD/PGFA逻辑门及其内部RAM容量越来越大,性能也越来越高是分不开的,加之价格下跌,强大的可编程能力,使得CPLD/PGFA不仅可以实现一个高复杂高难度的系统,而且还能快速升级,提升系统性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章