基于锁相环(PLL)的频率合成器设计

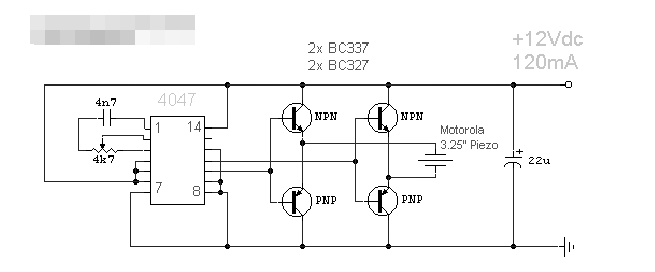

分享一种驱虫电路

如何实现高性能的锁相环(PLL)设计

提供显著跳频(FH)优势的下一代软件定义无线电收发器

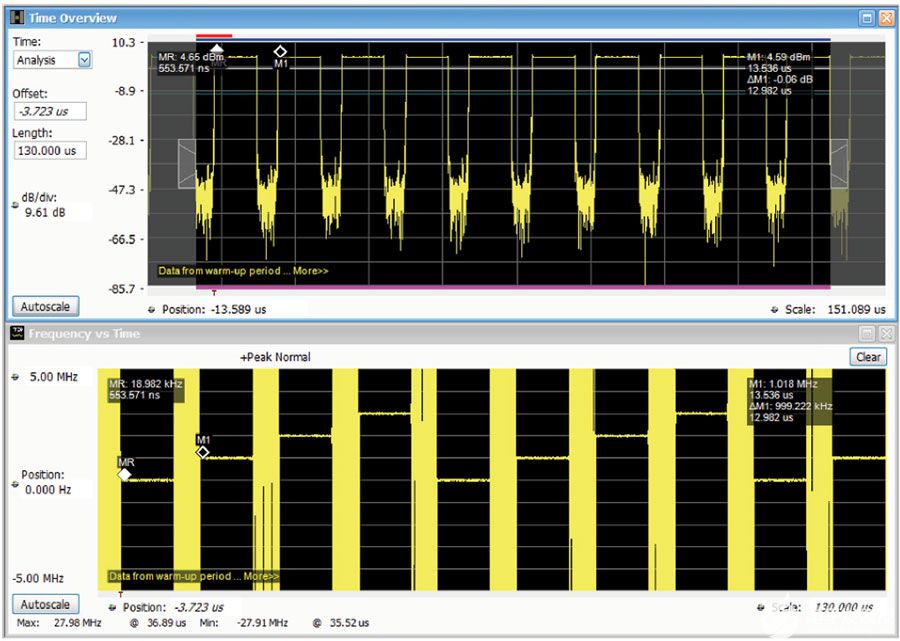

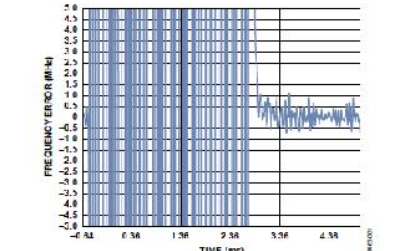

手动选择频段以缩短PLL锁定时间

集成单片PLL频率合成器芯片的原理、结构特点及应用分析

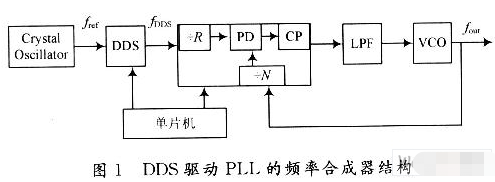

基于AD9954和ADF4113芯片实现频率合成器的设计

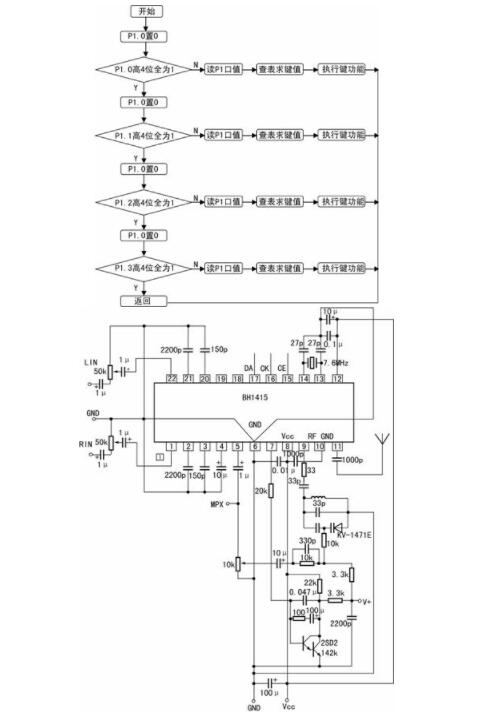

数控高保真PLL调频发射电路说明

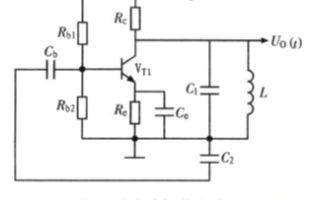

基于锁相环技术提高车辆探测灵敏度及抗干扰能力

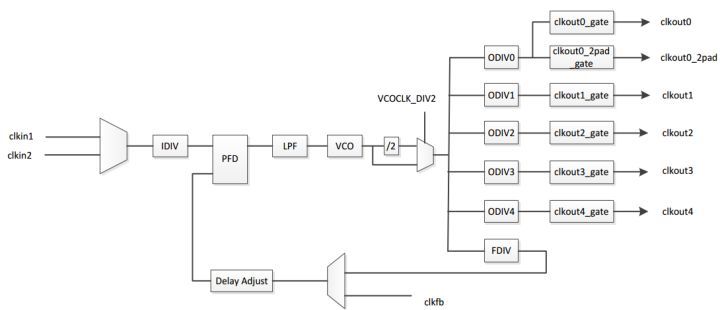

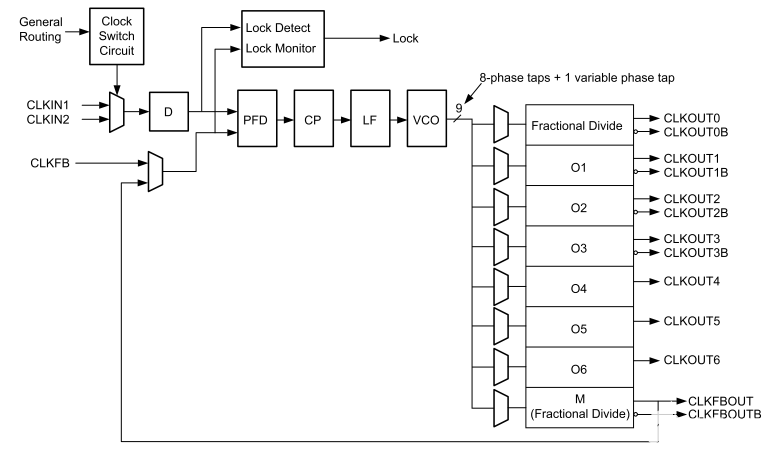

【紫光同创国产FPGA教程】【第四章】PDS下PLL实验

【ZYNQ Ultrascale+ MPSOC FPGA教程】第五章Vivado下PLL实验

锁相环频率合成器ADF4150HV的功能、优势及应用范围

同步降压型DC/DC控制器LTC3855的性能特点及应用范围

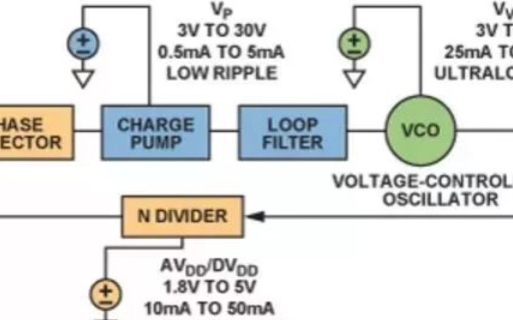

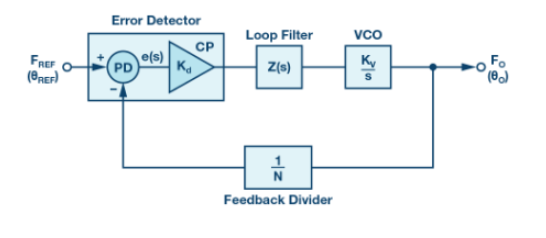

ADI ADF4xxx系列PLL经典数字PLL架构实现方案

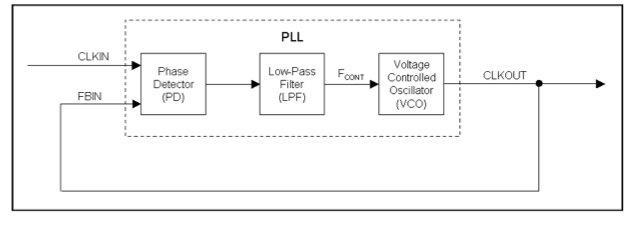

基于 PLL 的零延迟缓冲器的系统应用

LMK03000系列精密时钟调理器的性能及作用分析

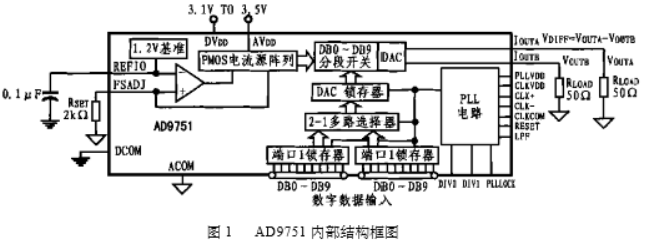

超高速10位CMOS D/A转换器AD9751的原理、特点及应用设计

ADMV8416/ADMV8432与PLL/VCO IC配合实现PLL/VCO技术的提升

提升PLL/VCO技术性能的方法

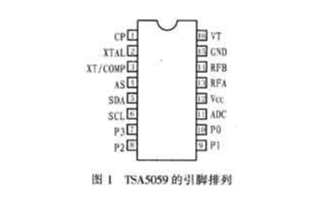

单片PLL频率合成器TSA5059的特点性能及典型应用电路