资料下载

×

如何使用FPGA实现16位RISC CPU的设计

消耗积分:0 |

格式:rar |

大小:0.39 MB |

2020-08-17

RISC_CPU 是一个复杂的数字逻辑电路,但是其基本部件的逻辑并不复杂,可以将其分成8 个基本部件来考虑:时钟发生器,指令寄存器,累加器,算术逻辑运算单元,数据控制器,状态控制器,程序计数器,地址多路器。各部件的连接关系见图1。其中时钟发生器利用外来时钟信号进行分频生成一系列时钟信号,送往其它部件用作时钟信号。各部件之间的相互操作关系则由状态控制器来控制。

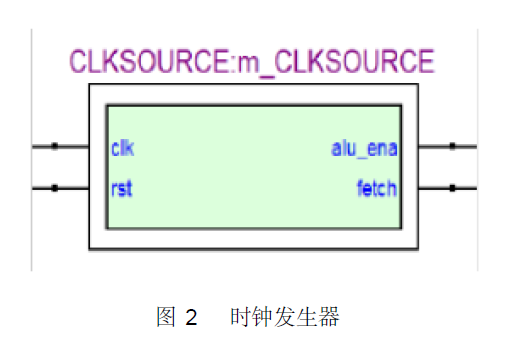

1. 时钟发生器

时钟发生器CLKSOURCE利用外来时钟信号clk 生成一系列时钟信号alu_clk,fetch, 并送往cpu 的其它部件。其中, fetch 是控制信号, clk 的6 分频信号。当fetch 高电平时,使clk 能触发cpu 控制器开始执行一条指令;同时fetch 信号还将控制地址多路器输出指令地址和数据地址。clk 信号还用作指令寄存器,累加器,状态控制器的时钟信号。图2 为时钟发生器原理图。时钟发生器的波形如图3 所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章