资料下载

使用FPGA设计的IO到底是什么

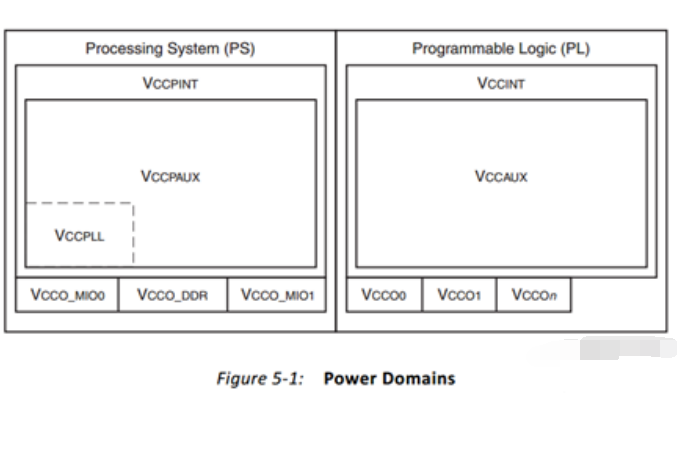

今天想和大家一起聊聊 FPGA 的 IO。先说说我当年入门的经历吧。国内的大学有 FPGA 开发条件的实验室并不太多,当年大学的那帮同学有的做 ARM,有的做 linux,很少有人做 FPGA,当时学 FPGA 仅仅是由于非常渴望的好奇心。所以,在淘宝买了一块开发板,就开始了自己的 FPGA 之路。大部分开发板的内容主要是教学员怎么样写 Verilog 代码,很少会对 FPGA 的芯片架构做详细的说明和解读,所以当年面试的时候就碰到了一个很尴尬的事情,面试官第一个问题问的就是:用的是哪颗 FPGA,内核电压是多少?当时就懵了,虽然做了快一年 FPGA,我还没有关注过芯片的内核电压···。但其实熟悉 FPGA 的基本架构,了解 FPGA 的芯片内部资源真的很重要。虽然很多 FPGA 工程师都是写代码,但是作为硬件编程工程师,如果不熟悉 FPGA 的底层资源和架构,是很难写出高质量的代码——至少很难写出复杂逻辑的高质量代码,也很难站在系统的层面去考虑芯片的选型等问题。那熟悉 FPGA 架构,首先最主要的一点,我们先来了解 FPGA 的 IO。 FPGA 的 IO 命名。FPGA 芯片 IO 命名方式太多,管脚也多,让人感觉很乱。这是我当年的感觉,诸如会经常听到: A13,B14···BANK34,BANK12····MIO0,EMIO···。但这确实是 FPGA 的特点,FPGA 可以兼容多种不同的电压标准,也有丰富的 IO。首先,FPGA 的 IO 物理命名规则,也就是我们做管脚约束时候的命名,芯片通常是长方体或者正方体,所以命名通常采用字母+数字组合的方式,从上到下是字母(A,B,C,D```),从左到右是数字(1,2,3```),所以诸如:A13(见下图),就是图上标红的位置,这个是 xilinx 的一颗芯片示意图,其它厂商的 FPGA 芯片也类似。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章