资料下载

×

PLL频率合成器的主要构建模块详细资料说明

消耗积分:0 |

格式:pdf |

大小:0.43 MB |

2020-11-26

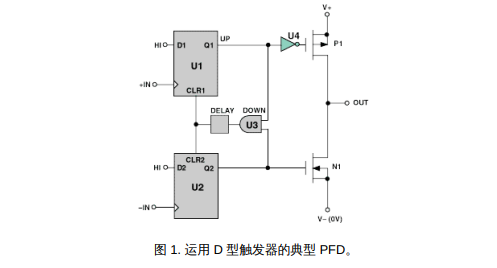

PLL 频率合成器基本构建模块 PLL 频率合成器可以从多个基本构建模块的角度来考察。我们在前面已经提到过这个问题,下面将更加详细地进行探讨:鉴频鉴相器(PFD) 参考计数器(R) 反馈计数器(N) 鉴频鉴相器(PFD) 频率合成器的核心是鉴相器,也称鉴频鉴相器。在鉴相器中,将比较参考频率信号与从 VCO 输出端反馈回来的信号,结果得到的误差信号用于驱动环路滤波器和 VCO。在数字 PLL (DPLL)中,鉴相器或鉴频鉴相器是一个逻辑元件。三种最常用的实现方法为:异或(EXOR)栅极 J-K 触发器数字鉴频鉴相器这里,我们只考虑 PFD,这也是 ADF4110 和 ADF4210 频率合成器系列中使用的元件,因为与 EXOR 栅极和 J-K 触发器不同,处于解锁状态时,其输出为频差以及两个输入间相差的函数。图 1 所示为 PFD 的一种实现方案,该类器件基本上由两个 D 型触发器组成。一路 Q 输出使能正电流源,另一路 Q 输出则使能负电流源。假设本设计中 D 型触发器由正边沿触发,则状态为(Q1, Q2): 11–两个输出均为高电平,由反馈至触发器上 CLR 引脚的 AND 栅极(U3)禁用。 00–P1 和 N1 均关闭,输出 OUT 实际处于高阻抗状态。 10–P1 开启,N1 关闭,输出位于 V+。 01–P1 关闭,N1 开启,输出位于 V–。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章