资料下载

×

基于可逆计数器的时序性总线硬件木马

消耗积分:0 |

格式:pdf |

大小:2.56 MB |

2021-03-19

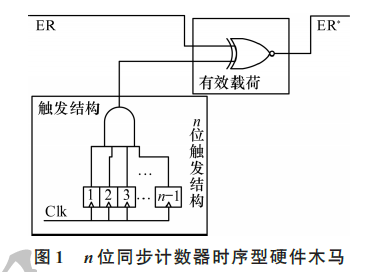

RS总线集成电路在航空航天及工业控制领域具有广泛的应用,随着集成电路硬件木马的检测成为研究热点,作为总线硬件木马研究领域的分支,其设计越来越受关注。在常规时序型硬件木马的基础上,针对RS232总线集成电路,设计一种基于可逆计数器的时序型总线硬件木马。采用Xiix公司的ISE软件在RTL层设计相应的RS232总线 Verilog代码,并在常规和可逆时序型硬件木马触发阈值呈等差递增的条件下进行 Modelsim仿真分析结果表明,在总线功能需求复杂和传输数据较多的情况下,可逆时序型木马比常规时序型硬件木马具有灵活性和较低的触发率,隐蔽性更强。

、

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章