资料下载

硬件描述语言Verilog HDL

详细介绍了verilog语言,很容易看懂,并配有示例

一、什么是Verilog HDL

Verilog HDL是一种用于数字逻辑电路设计的硬件描述语言(Hradware Description Language ),可以用来进行数字电路的仿真验证、时序分析、逻辑综合。

用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。

Verilog HDL 既是一种行为描述语言也是一种结构描述语言。

既可以用电路的功能描述,也可以用元器件及其之间的连接来建立Verilog HDL模型。

二、Verilog HDL的发展历史

1983年,由GDA(GateWay Design Automation)公司的Phil Moorby首创;

1989年,Cadence公司收购了GDA公司;

1990年, Cadence公司公开发表Verilog HDL;

1995年,IEEE制定并公开发表Verilog HDL1364-1995标准;

1999年,模拟和数字电路都适用的Verilog标准公开发表

三、不同层次的Verilog HDL抽象

Verilog HDL模型可以是实际电路的不同级别的抽象。抽象级别可分为五级:

系统级(system level): 用高级语言结构实现的设计模块外部性能的模型;

算法级(algorithmic level): 用高级语言结构实现的设计算法模型;

RTL级(register transfer level): 描述数据在寄存器之间流动和如何处理这些数据的模型;

门级(gate level): 描述逻辑门(如与门、非门、或门、与非门、三态门等)以及逻辑门之间连接的模型;

开关级(switch level): 描述器件中三极管和储存节点及其之间连接的模型。

四、Verilog HDL的特点

语法结构上的主要特点:

形式化地表示电路的行为和结构;

借用C语言的结构和语句;

可在多个层次上对所设计的系统加以描述,语言对设计规模不加任何限制;

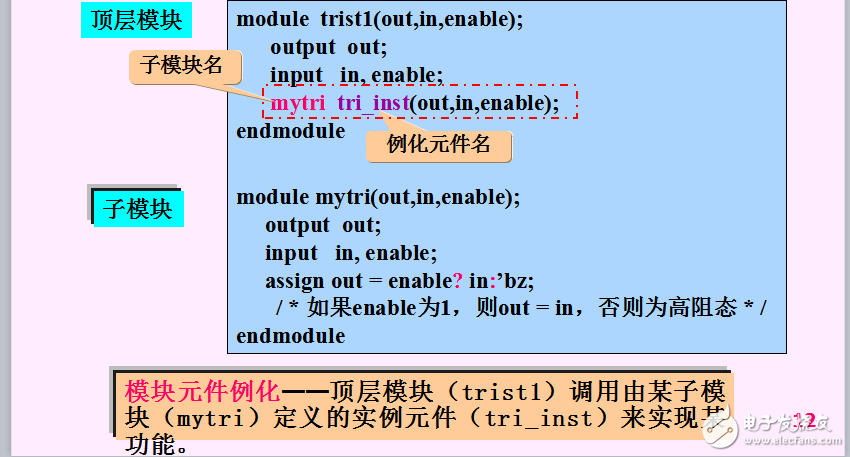

具有混合建模能力:一个设计中的各子模块可用不同级别的抽象模型来描述;

基本逻辑门、开关级结构模型均内置于语言中,可直接调用;

易创建用户定义原语(UDP,User Designed Primitive) 。

易学易用,功能强

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章