资料下载

×

DSP存储器共享与快速访问技术

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-10-23

本文介绍了在多个DSP之间或者DSP与其他CPU之间存储器共享技术的基本设计方法,重点介绍了如何在设计上提高存储器的访问速度和克服访问竞争的方法。

在多任务信号处理系统中,为了提高信号的处理速度,往往使用几个DSP协同工作,为此,必须要解决好几个DSP对共享存储器的高速访问问题。具体来说,主要要解决好两个问题:

(1)通过建立竞争仲裁机制解决存储器访问共享竞争问题;

(2)解决批量数据高速访问问题。DSP对批量数据的访问一般都是通过启动DMA完成,而DMA一旦启动,数据的传输就不受DSP控制,因此,要设计专门控制电路和缓冲区来确保高速数据传输的稳定性和可靠性。

本文重点介绍了两个TMS320C5402之间共享SRAM和DDRSDRAM的设计方法。

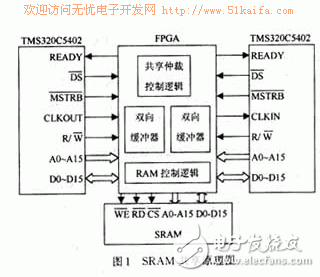

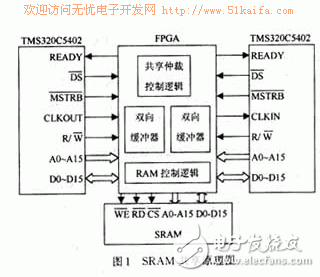

1 SRAM的共享访问

图1是2片TMS320C5402共享SRAM的原理图。为了保证对SRAM访问的可靠性,2片DSP共用同一个系统时钟和具有相同的访问优先级。当2片DSP同时对共享存储器发出访问需求时,FPGA中的共享仲裁控制逻辑会在第1个存储器访问周期允许第1片DSP对SRAM进行访问,同时向第2片DSP发出READY等待信号,然后在下一个存储器访问周期撤销该等待信号,允许第2片DSP对SDRAM进行访问。如果进行批量数据传输,则2片DSP对应的READY信号会交替启动。FPGA中的2个双向缓冲器是互相禁止的。另外,在DSP的软件编程时要注意,在软件等待周期寄存器被写入后至少要等待2个时钟周期DSP才会启动对READY信号的检测。

2 DDRSDRAM的高速共享访问

在上述方式中,如果2片DSP同时要对共享存储器进行访问,其访问速度将会降低一倍。在实际的信号处理系统中,特别是在连续视频信号的编码、压缩与速访问,如果采用大容量双口RAM,其硬件成本开销太大。现在PC机中大量使用的双速数据同步动态存储器(Double Data Rate Synchronous,DRAM)具有存储容量大、访问速度快、价格低廉等特点,因此在大容量高速数字信号处理系统中,只要解决好对DDRSDRAM的读写访问控制问题,就能解决好大容量高速存储器的共享访问问题。

2.1 DDRSDRAM的读写访问特性

图2为现代公司的HY5DV651622双速同步动态存储器的功能框图。其存储容量为8 Mb,数据宽度为16 B,分为4个页面,采用行列地址复用方式。在时钟的上升和下降沿均可以进行数据的读写操作。对DRAM的控制包括命令控制和数据读写控制,在命令控制中主要包括模式寄存器设置、存储器自动刷新控制等,通过模式寄存器的设置可以使存储器工作于猝发读写方式,读写长度可以达到256个地址。

在多任务信号处理系统中,为了提高信号的处理速度,往往使用几个DSP协同工作,为此,必须要解决好几个DSP对共享存储器的高速访问问题。具体来说,主要要解决好两个问题:

(1)通过建立竞争仲裁机制解决存储器访问共享竞争问题;

(2)解决批量数据高速访问问题。DSP对批量数据的访问一般都是通过启动DMA完成,而DMA一旦启动,数据的传输就不受DSP控制,因此,要设计专门控制电路和缓冲区来确保高速数据传输的稳定性和可靠性。

本文重点介绍了两个TMS320C5402之间共享SRAM和DDRSDRAM的设计方法。

1 SRAM的共享访问

图1是2片TMS320C5402共享SRAM的原理图。为了保证对SRAM访问的可靠性,2片DSP共用同一个系统时钟和具有相同的访问优先级。当2片DSP同时对共享存储器发出访问需求时,FPGA中的共享仲裁控制逻辑会在第1个存储器访问周期允许第1片DSP对SRAM进行访问,同时向第2片DSP发出READY等待信号,然后在下一个存储器访问周期撤销该等待信号,允许第2片DSP对SDRAM进行访问。如果进行批量数据传输,则2片DSP对应的READY信号会交替启动。FPGA中的2个双向缓冲器是互相禁止的。另外,在DSP的软件编程时要注意,在软件等待周期寄存器被写入后至少要等待2个时钟周期DSP才会启动对READY信号的检测。

2 DDRSDRAM的高速共享访问

在上述方式中,如果2片DSP同时要对共享存储器进行访问,其访问速度将会降低一倍。在实际的信号处理系统中,特别是在连续视频信号的编码、压缩与速访问,如果采用大容量双口RAM,其硬件成本开销太大。现在PC机中大量使用的双速数据同步动态存储器(Double Data Rate Synchronous,DRAM)具有存储容量大、访问速度快、价格低廉等特点,因此在大容量高速数字信号处理系统中,只要解决好对DDRSDRAM的读写访问控制问题,就能解决好大容量高速存储器的共享访问问题。

2.1 DDRSDRAM的读写访问特性

图2为现代公司的HY5DV651622双速同步动态存储器的功能框图。其存储容量为8 Mb,数据宽度为16 B,分为4个页面,采用行列地址复用方式。在时钟的上升和下降沿均可以进行数据的读写操作。对DRAM的控制包括命令控制和数据读写控制,在命令控制中主要包括模式寄存器设置、存储器自动刷新控制等,通过模式寄存器的设置可以使存储器工作于猝发读写方式,读写长度可以达到256个地址。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章