资料下载

×

三维芯片的垂直互连

消耗积分:1 |

格式:rar |

大小:0.57 MB |

2017-11-22

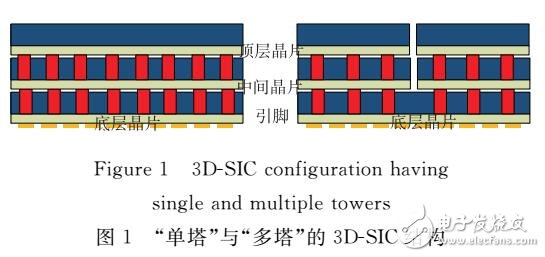

三维芯片( 3DSIC)通过硅通孔TSV技术实现电路的垂直互连,有效提高了系统集成度和整体性能。由于三维芯片测试中,用于测试的引脚数和TSV数目以及测试时功耗的限制都对测试时间有很大的影响,拟提出一种装箱问题思想的测试方案,针对每层只有一个晶片的“单塔”结构和每层有多个晶片的“多塔”结构进行测试调度优化。该优化方案在控制测试引脚数、测试TSV数目与测试功耗的同时,能有效缩短测试时间。实验结果表明,与同类方案相比,在多种限制条件和不同结构中,都有着显著的优化结果。其中“单塔”最高优化45. 28%的测试时间,“多塔”最高优化了27. 78%的测试时间。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章