资料下载

×

JESD204B-01协议规范的详细资料说明

消耗积分:1 |

格式:pdf |

大小:2.62 MB |

2019-04-16

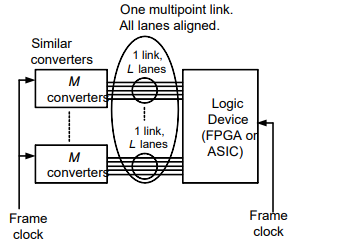

本规范描述了数据转换器和逻辑设备之间的串行接口。它包含规范性信息,使设计人员能够实现与本规范涵盖的其他设备通信的设备。包括资料性附录,以澄清和举例说明规范。

由于涉及的应用范围,本文档的目的是完全指定串行数据接口和链路协议。接口和设备功能共用的某些信号,如设备时钟和控制接口,具有应用相关的要求。设备也可能具有与应用程序相关的模式,例如会影响接口的低功率/关机模式。在这些情况下,规范仅约束与接口相关的其他设备属性,并将特定的实现留给设计器。

标准的修订版A被扩展到支持串行数据接口,每个转换器设备由单个或多个通道组成。此外,转换器功能(ADC或DAC)可以分布在多个设备上:

•所有并行运行设备均采用相同的数据格式实现或指定为彼此同步运行。

•通常这意味着它们是同一产品系列的一部分。

本标准的B版现在支持以下附加功能:

•通过JESD204链路实现可重复、可编程确定性延迟的机制。

•支持高达12.5 Gbps的串行数据速率。

•从使用帧时钟作为主时钟源过渡到使用设备时钟作为主时钟源。与需要帧时钟输入相比,设备时钟频率要求提供了更大的灵活性。

逻辑设备(如ASIC或FPGA)始终假定为单个设备。

图1比较了最初的JESD204规范及其修订版的范围。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章