资料下载

Cortex M0内核的特性比较和兼容性与架构等详细资料说明

Cortex-M内核共同特性

针对微控制器应用

对功耗和硅片面积进一步优化

更适合低成本和低功耗的应用

发生中断和异常时自动保存现场

进出异常处理的软件开销很小

确定的指令执行时间

从确定性存储器运行代码时,指令执行的时间总是相同

Cortex-M系列的软件兼容性

向上路径(M0-》M3-》M4)的移植直接了当

Cortex-Mx内核的指令集是Cortex-My内核(x《y)指令集的子集。软件可以直接移植过去,性能则随着MCU时钟频率的提高以及冯诺依曼到哈佛架构的改进而得到提升

推荐对代码进行重新编译

从M0内核升级到M3内核:重新编译可以充分利用更高效的指令,比如硬件除法

从M0/M3内核升级到带FPU的M4内核:某些代码需要使用intrinsic重新编写,以利用M4内核高级的DSP/SIMD指令

对于STM32家族内的产品,丰富的外设也相互兼容以保证移植的顺畅

向下路径(M3-》M0)的移植需要注意

M0内核的NVIC和SCB寄存器只能字访问,M3可支持字、半字、字节访问

M3内核的某些NVIC和SCB寄存器在M0中没有

Interrupt Active Status Register

Software Trigger Interrupt Register

Vector Table Offset Register

某些 fault status registers

如果使用了汇编,某些指令不再被M0支持;对于C代码,某些指令如硬件除法,编译器会自动调用C库函数来处理除法操作

M0不支持非对齐数据传输

M0不再具有M3所支持的位带操作

使用用户线程模式和MPU特性的应用则不能移植到M0内核上

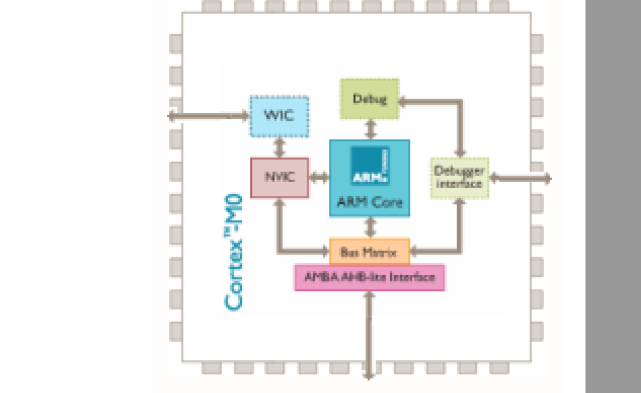

Cortex-M0处理器的微架构

ARMv6M架构

Thumb-2指令

集成可配置的NVIC

和Cortex-M3兼容

微处理器架构

带跳转预测的3级流水线

1条 AHB-Lite总线接口

可配置的超低功耗模式

深度睡眠、唤醒中断控制器

针对广泛应用的灵活配置

可配置的中断控制器(带优先级的最多32个中断)

不带内存保护单元MPU

可选的调试&跟踪功能

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章