资料下载

怎样才能测试PCIE物理层详细资料简介

从2004年Intel的Grantsdale芯片组首次引入PCI Express (简称PCle)以来,PCIe 在计算机和通讯产品上得到了广泛的应用。PCle首先被用到了MCH (Memory Controller Hub)和显卡的接口,取代旧的AGP总线,而且,MCH和ICH (I/O Controller Hub)的连接也使用了PCle总线,此外,很多要求高速数据传输的插卡比如数据采集卡、千兆网卡等也采用了PCle总线,替代了原来的PCI总线。

第一代的PCle速率为2.5Gbps, - -对发送的差分信号和-对接受的差分信号组成- -路信道,可以实现大约250MByte/s的数据传输率, PCle的显卡使用了16 路信道(又称为PClex16),可以实现250M*16=4GByte/s的数据传输率,能满足看高清电影或者玩3D游戏时大量图像数据在显卡与MCH间收发的要求,而一些数据速率要求不高的外设,比如千兆以太网卡,通常是一路PCle的接口(PClex 1)。

第二代的PCle的速率高达5Gbps,是PCle一代的2倍,在2007年,新的计算机主板芯片组和显卡都已升级到了PCle二代。

并行信号VS串行信号

在十年前,并行信号在电路板上非常流行,比如PCI、ISA、 AGP、GMII等等。并行信号中通常包括了一路时钟和多路数据信号,为了满足建立保持时间的时序要求,通常要求时钟和数据信号的走线等长,这样就增加了印刷电路板(PCB)的设计难度以及面积,而且,多路并行信号在传输中,信号间的串扰导致信号质量恶化,同步或奇偶模式开关时会减小建立保持时间的余量,多种原因导致并行信号无法适应高速数据的传输。

PCle信号是串行的差分信号,相比并行信号,串行信号的数据内嵌时钟,在接受端可以使用时钟恢复电路从串行数据信号中恢复时钟,然后用时钟来同步数据:由于不存在时钟和数据同步的时序问题,串行信号的速率通常都在GHz以上,一对高速差分信号的传输速率可以快于多路低速的并行信号:面且差分信号在传输的时候,抗干扰能力更强,对其他信号的串扰也小于单端信号;综合这些因素,串行的差分信号在计算机、通讯、消费电子类产品上越来越普及,传输速率也会越来越快。

PCIe的物理层测试

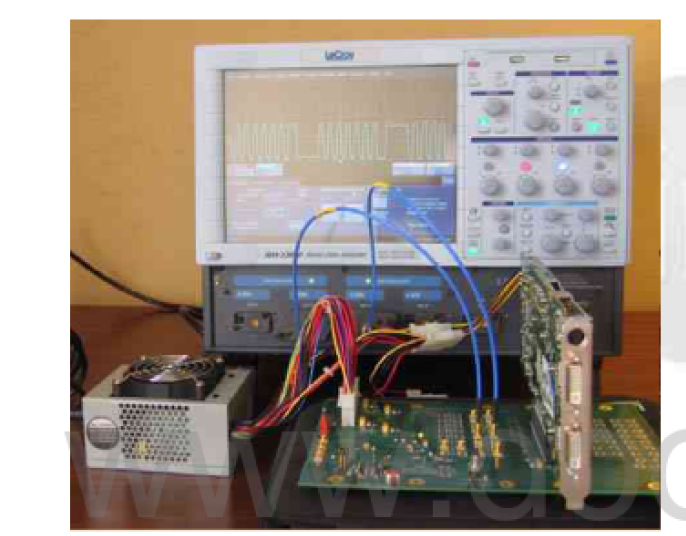

对于串行差分信号的物理层测试,通常需要测试眼图、抖动、比特率、上升下降时间等等。PCle的官方组织PCISIG对PCIe的物理层测试做了详细的规定。

对于PCle一代信号的测试,通常需要6GHz以上带宽的示波器,对于PCle二代的测试,通常需要12.5GHz以上带宽的示波器。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章