资料下载

使用51单片机和EPM7128设计实现简易逻辑分析仪的论文免费下载

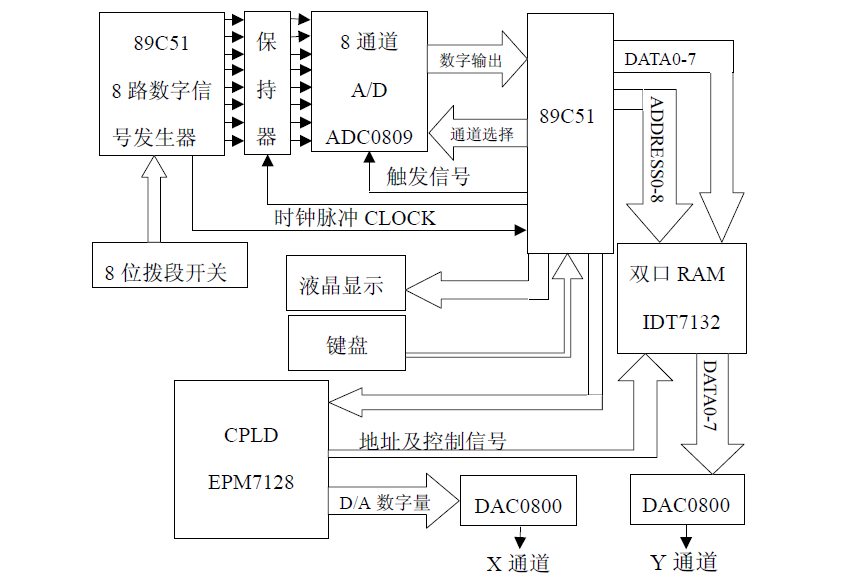

本设计采用单片机(89C51)和可编程逻辑器件(EPM7128)作为系统的控制核心。整个设计采用了模块化的设计思想,包括数字信号发生器、采样保持电路、逻辑信号门限电压比较、信号采集与存储、示波器X-Y通道控制、触发点与时间标志线控制、D/A转换、液晶显示、控制面板等功能模块。数字信号发生器由单片机读取8个外部开关状态,经循环移位输出。单片机检测8通道输入,在满足触发条件时,进行一次采样和存储,输入经采样保持器LF398,既可以满足对8路信号的A/D转换为同一时刻的数据,又可以提高输入阻抗。CPLD一方面控制存储器里的数据输出,经DAC0800转换为模拟电压后作为示波器的Y通道输入;另一方面由CPLD产生8位的循环递增数字信号,经DAC0800转换为模拟电压后,其电压波形为锯齿波,将它作为示波器的X通道输入。存储器采用双口RAM(IDT7132),这样可较简单的实现单片机与CPLD之间的通信。整个系统较好的实现了题目的要求,达到了较高的性能指标。

1、数字信号发生器模块

方案一:采用74LS199产生8路数字信号。74LS199是具有串行/并行输入及并行/串行输出的8位移位寄存器。利用74LS199的并行置数功能可实现逻辑信号的预置;利用74LS199的移位功能可实现逻辑信号的循环、重复输出。但此方案控制复杂,且需频率为100Hz的时钟,不易采用。

方案二:采用单片机编程实现序列信号发生器。通过8路拨段开关来设定要产生的序列信号,单片机读取这8路信号,经过处理,产生循环移位序列,且单片机定时精确。此方案简单可行。故我们采用了方案二。

2、 8位输入、触发电路

方案一:采用8片模数转换器同时对8路信号进行采集,然后将采集到的数据用单片机与转换成数字量的逻辑门限电压进行比较以决定其逻辑。 16级逻辑门限可由键盘输入。此方案能实时的对信号进行采集、比较和存储。但需要的AD芯片较多,不宜采用。

方案二:将8路输入信号通过8个比较器进行比较,比较器的基准电压可以接到DAC0832的输出端,单片机根据所需的逻辑门限电压,将其对应的数字量发送给DAC0832,在DAC0832的输出端即可得到所需的逻辑门限电压,可较好的实现16级逻辑门限的变化。此方案可实现题目的要求,但所用器件较多,且占用单片机较多的I/O口,故未采用。

方案三:将8路输入信号先用采样保持器LF398进行保持,以保证A/D转换的8路数据为同一时刻的数据,然后使用8通道A/D转换器ADC0809顺序采集保持在LF398中的数据,并用单片机判断其逻辑。逻辑门限电压由键盘输入给单片机,实现题目要求的16级门限变化。此方案容易控制,实现简单。故我们采用此方案。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章