资料下载

如何设计一种低功耗无片外电容LDO

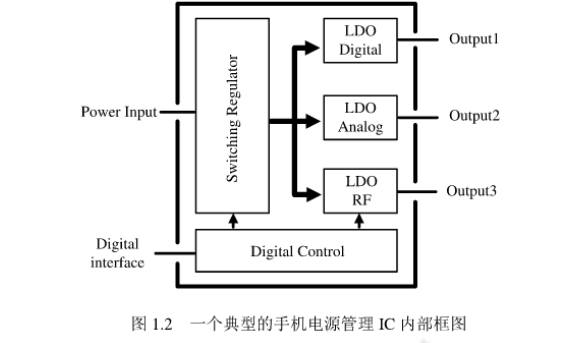

近年来随着便携式电子产品的迅速普及,电源管理芯片需求急剧增加。电源管理的主要目的是提高功率器件的效率,从而延长电池寿命和设备的使用时间。作为电源管理芯片中最为常见的产品,低压差线性稳压器,即LDO (low dropout regulator),由于具有电路简单,低噪声及低功耗的优点,因此获得了广泛的应用。然而,传统的LDO需要外接片外大电容,这样一方面增加了PCB (Printed Circuit Board)的面积;另一方面也增加了芯片的应用成本,而且也难于在SOC (System on Chip)芯片中使用。因此,无片外电容LDO成为业界关注的热点。 无片外电容LDO的设计存在两个难点。首先,传统LDO环路主极点位于输出节点,利用外接大电容的等效电阻产生一个左半平面零点进行频率补偿,而无片外电容LDO的环路稳定性就必须重新考虑。其次,当LDO的负载电流发生瞬态跳变时,传统LDO主要利用片外电容进行充放电,以减小输出电压的过冲和尖峰。但对于无片外电容LDO,就必须通过提高环路的响应速度来提高瞬态响应速度,但单纯提高带宽会导致电路功耗的增加。因此,业界通常会设计一个摆率增强模块,在负载电流突变时大幅度增加误差放大器的摆率,以提高LDO的瞬态响应速度;而在正常供电时,摆率增强模块不工作,以节省功耗。本文首先在这两个方面做了深入调研,对前人提出的结构和电路进行讨论分析,在此基础上提出了新的电路结构。 本论文所设计的低功耗无片外电容LDO用于为一款低功耗SIGMA-DELTA ADC中的数字电路供电。电路基于MXIC0.35μm标准CMOS工艺实现,设计输出电压3.3V,最大负载电流5mA,电源电压在2.7V~5.5V之间变化。整体电路分为带隙基准源和LDO主体电路两部分,带隙基准源为LDO提供一个与温度及电源无关的参考电压。其中带隙基准源为低功耗结构,电流消耗仅为12μA。LDO主体电路中设计了一个摆率增强模块,可以大大增加负载电流瞬态突变时误差放大器的摆率,有效提高了LDO的瞬态响应速度,从而降低了输出电压的尖峰和过冲。与相关文献中的LDO相比,本文设计的LDO其摆率增强模块具有结构简单,性能良好的特点。另外,通过将误差放大器偏置在亚阈值区,有效降低了整体电路的功耗。通过利用CADENCE仿真验证,本文设计的LDO压差电压低于100mV,LDO电路的电流消耗为31μA,负载电流瞬态突变时输出电压尖峰小于100mV,满足应用要求。+

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章