资料下载

无片外电容的LDO线性稳压器的设计说明

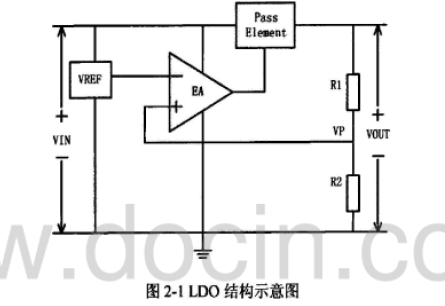

越来越多的功能被集成到芯片、印刷电路板和电子器件中,每个模块都需要专门的稳压器供电。传统低压差线性稳压器(LDO)需要外接一个较大的微法量级的片外电容,依靠输出端外接电容的串联等效电阻(ESR)为系统补偿第一个次极点,以保持系统的稳定性。

本文提出了一个无片外电容的LDO线性稳压器的结构的解决方案。去掉了传统的LDO所使用的较大的片外电容,减小了板上面积及成本,同时也减少了芯片引脚,提高了电源管理系统的集成度。仿真结果表明,电路在0-100mA负载电流范围内的相位裕度均大于60度,增益裕度大于10dB,同时具有较好的负载瞬态响应,在1kHz的PSRR为57dB,100kHz的PSRR为50dB。整体面积为0.22mm2,静态电流为200uA。

本设计首先根据系统要求提出设计指标,然后在分析电路工作原理及性能参数的基础上,重点解决了稳定性及瞬态响应存在的问题,接着给出电路晶体管结构,进行详细的仿真及优化。最后完成版图设计和物理验证,交付代工厂流片并测试。

本文的设计重点在于去掉片外电容之后,解决电路在全负载范围内的稳定性及瞬态响应问题。提出了一个快速通路作为补偿电路,保证其瞬态响应以及稳定性。同时设计了过压保护电路来防止输出电压过高对晶体管的影响。

本芯片已在SMIC0.13um流片成功并测试,能够以IP在其他不同应用中使用,可以根据不同的需求调整电路的驱动能力,降低电路的功耗及而积,提高电路的效率。

本文着眼于无片外电容LDO线性稳压器的设计,在设计过程中降低了功耗与面积,研究成果对无片外电容LDO的电路设计、版图设计有很好的参考价值,为SoC设计提供一定的借鉴意义。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章