资料下载

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十九章Hello World(下)

作者:ALINX

* 本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

此文基于第十八章内容进行软件开发

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十八章Hello World(上)

软件工程师工作内容

Vitis工程目录为“ps_hello/vitis”

以下为软件工程师负责内容。

1.Vitis调试;

2.创建Application工程;

1)新建一个文件夹,将vivado导出的xx.xsa文件拷贝进来;

2)Vitis是独立的软件,可以双击Vitis软件打开;

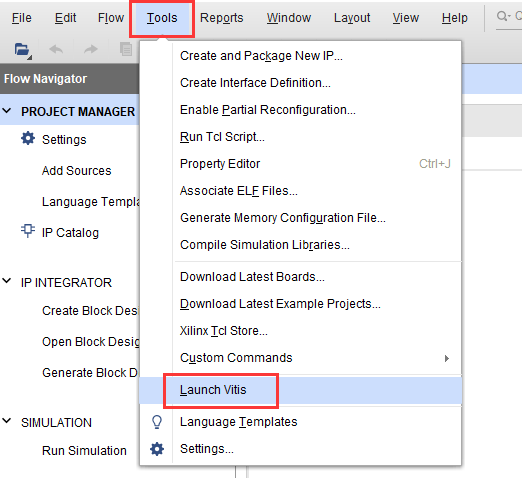

也可以通过在Vivado软件中选择ToolsLaunch Vitis打开Vitis软件

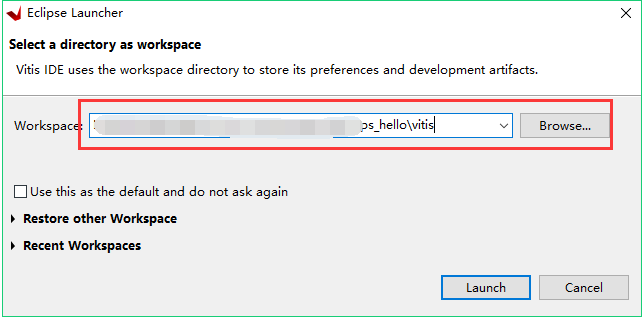

选择之前新建的文件夹,点击”Launch”

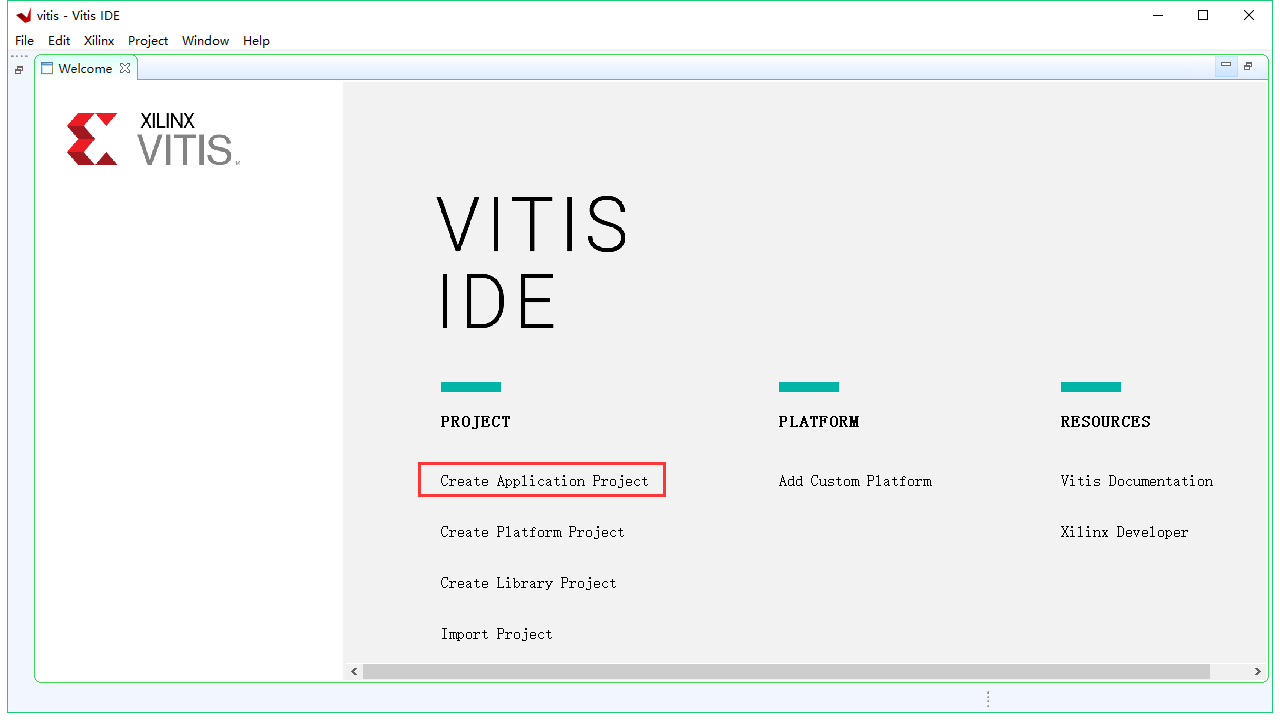

3)启动Vitis之后界面如下,点击“Create Application Project”,这个选项会生成APP工程以及Platfrom工程,Platform工程类似于以前版本的hardware platform,包含了硬件支持的相关文件以及BSP。

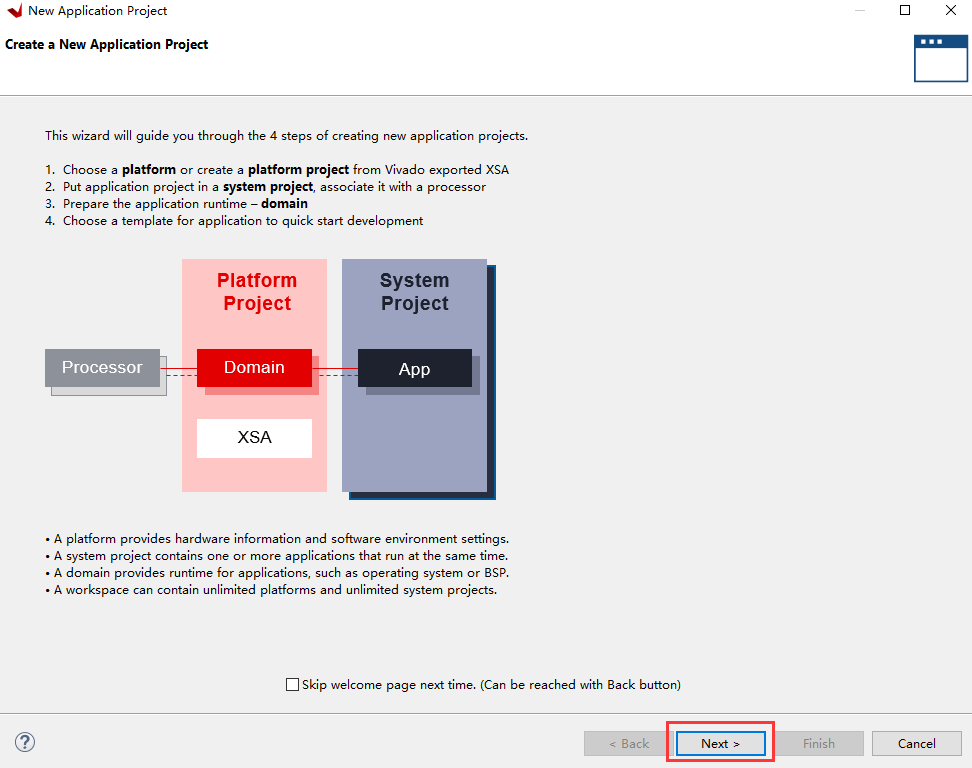

4)第一页为介绍页,直接跳过,点击Next

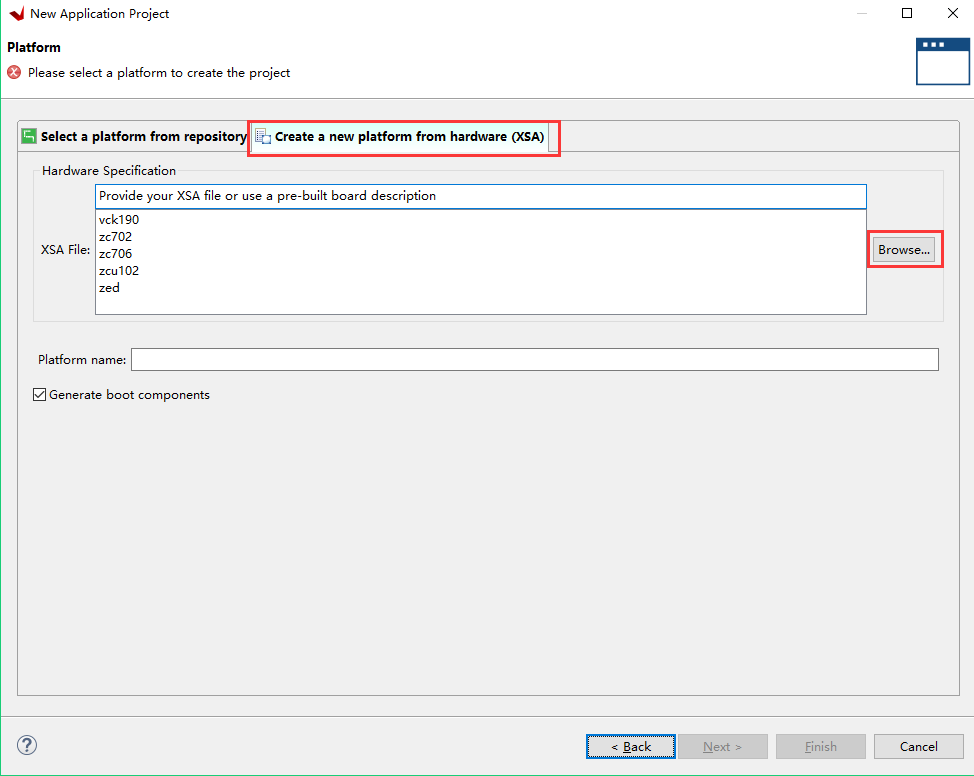

5)选择“Create a new platform from hardware(XSA)”,选择“Browse”

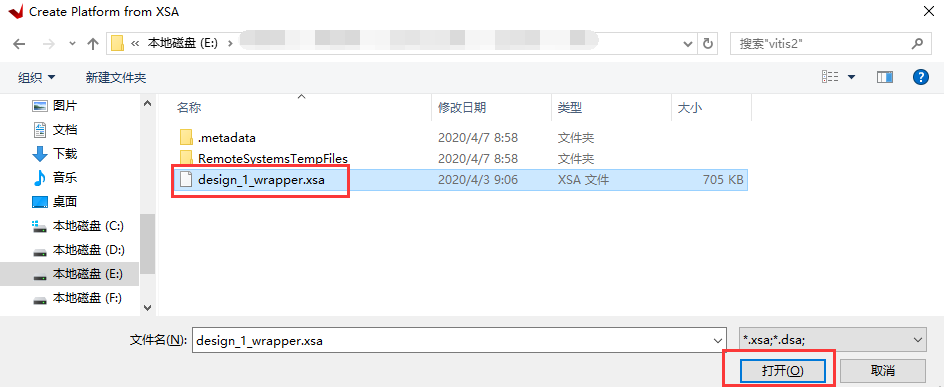

选择之前生成的xsa,点击打开

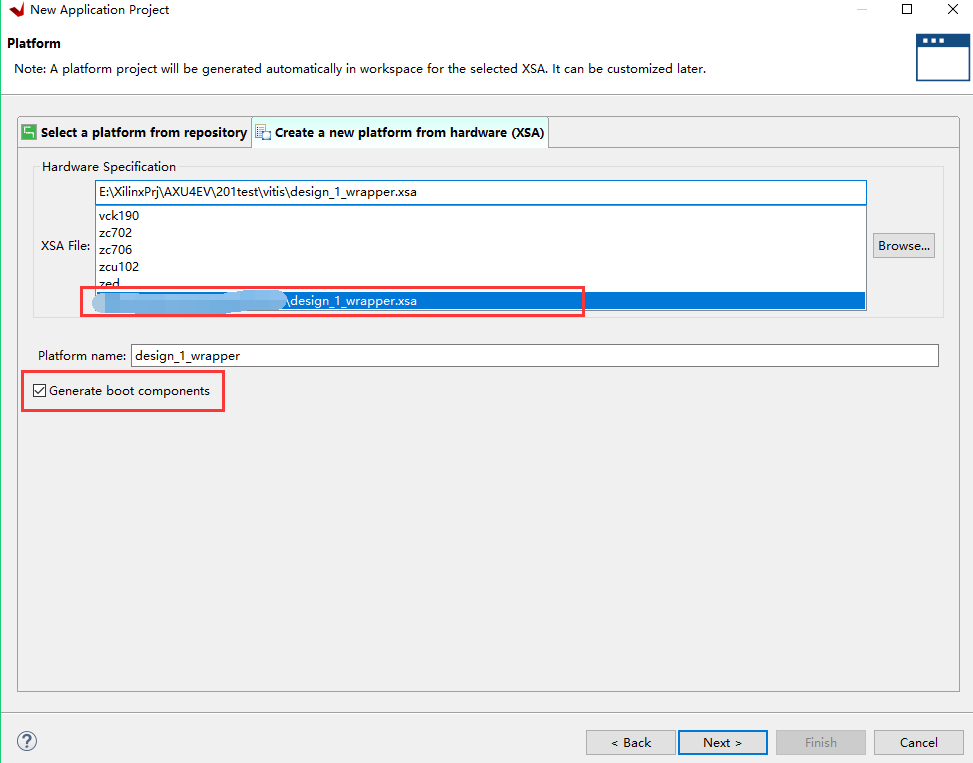

6)最下面的Generate boot components选项,如果勾选上,软件会自动生成fsbl工程,我们一般选择默认勾选上。

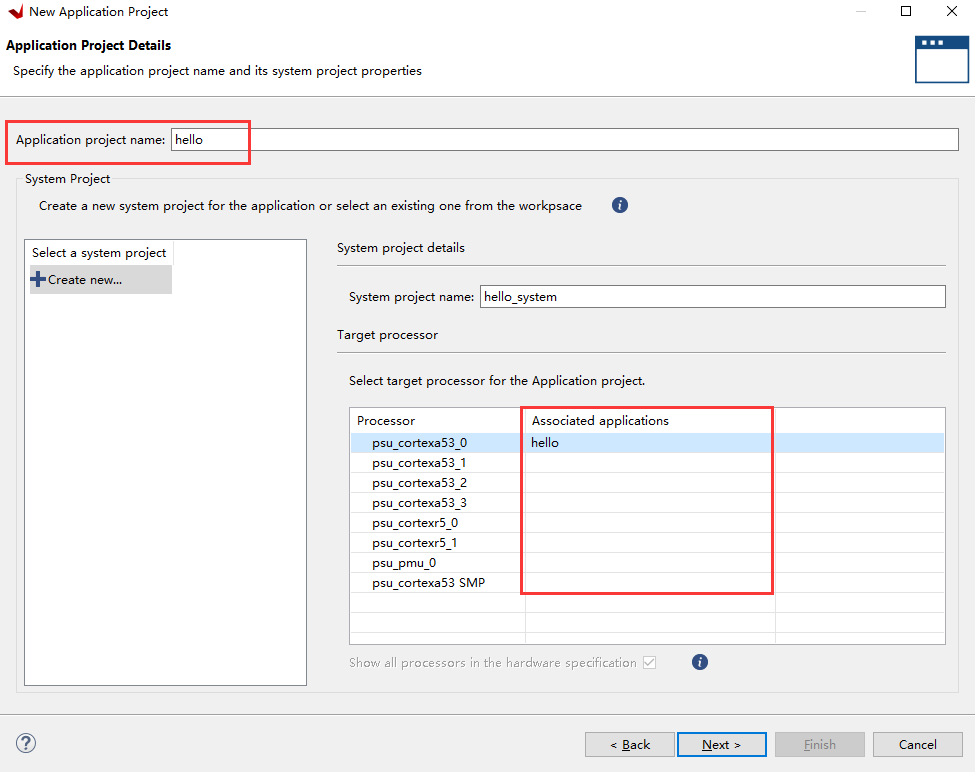

7)填入APP工程名称,在方框处点击可以选择对应的处理器,我们这里保持默认

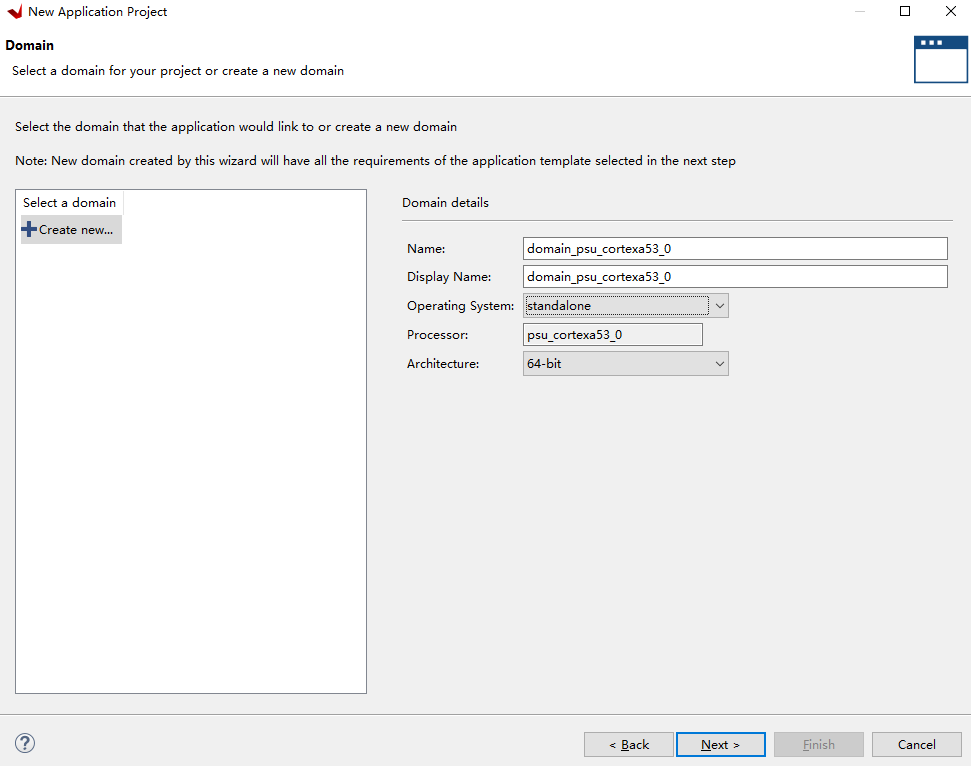

8)在这个界面可以修改Domain名称,选择操作系统,ARM架构等,这里保持默认,操作系统选择standalone,也就是裸机。

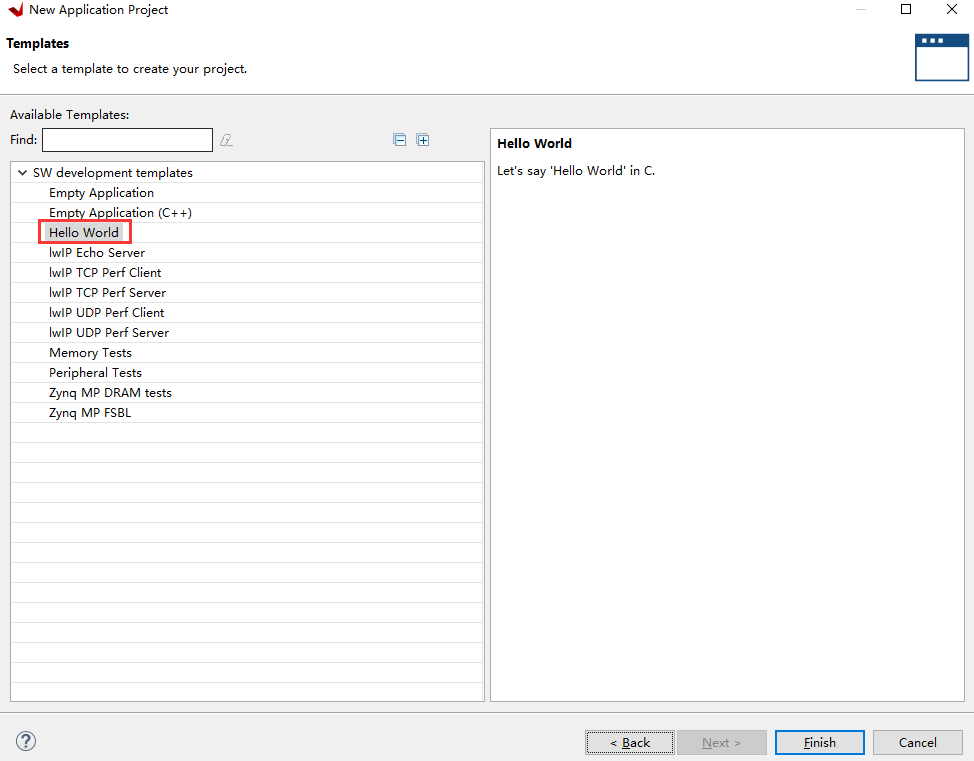

9)选择”Hellow World”模板,点击“Finish”完成

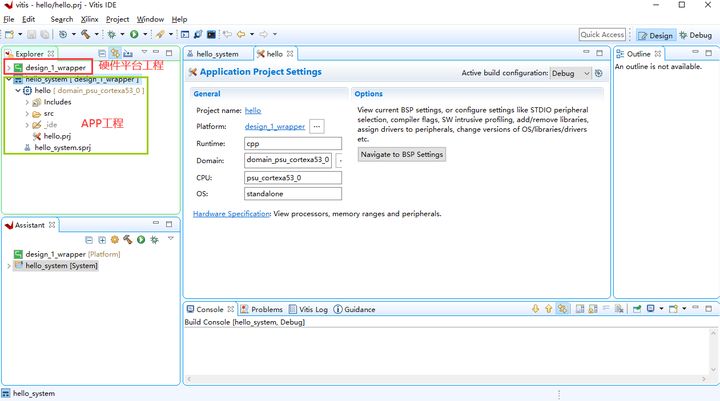

10)完成之后可以看到生成了两个工程,一个是硬件平台工程,即之前所说的Platfrom工程,一个是APP工程

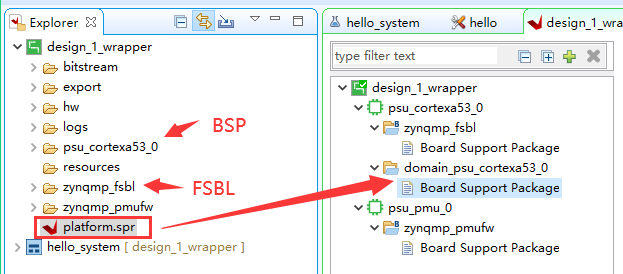

11)展开Platform工程后可以看到里面包含有BSP工程,以及zynq_fsbl工程(此工程即选择Generate boot components之后的结果),双击platform.spr即可看到Platform对应生成的BSP工程,可以在这里对BSP进行配置。软件开发人员比较清楚,BSP也就是Board Support Package板级支持包的意思,里面包含了开发所需要的驱动文件,用于应用程序开发。可以看到Platform下有多个BSP,这是跟以往的SDK软件不一样的,其中zynqmp_fsbl即是fsbl的BSP,domain_psu_cortexa53_0即是APP工程的BSP。也可以在Platform里添加BSP,在以后的例程中再讲。

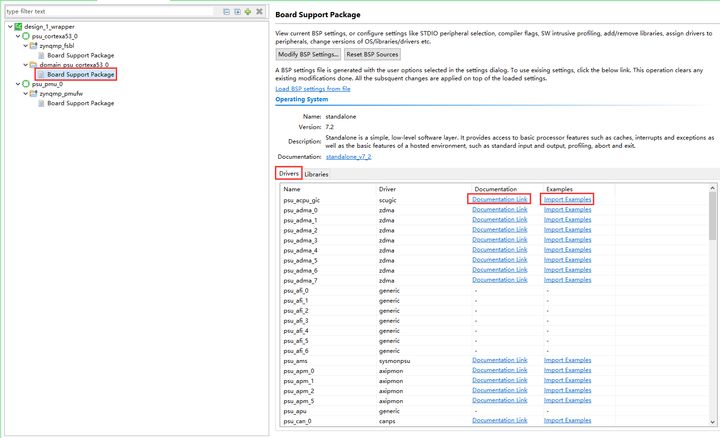

12)点开BSP,即可看到工程带有的外设驱动,其中Documentation是xilinx提供的驱动的说明文档,Import Examples是xilinx提供的example工程,加快学习。

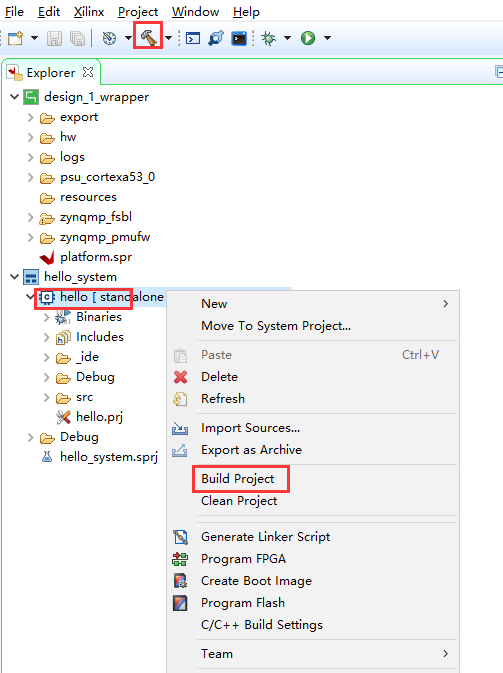

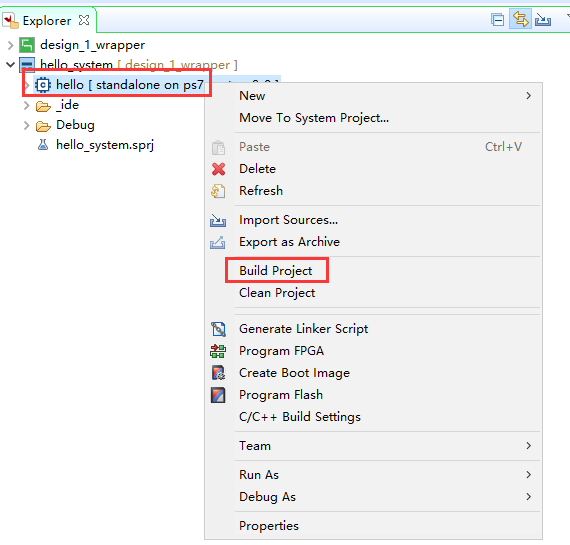

13)选中APP工程,右键Build Project,或者点击菜单栏的“锤子”按键,进行工程编译

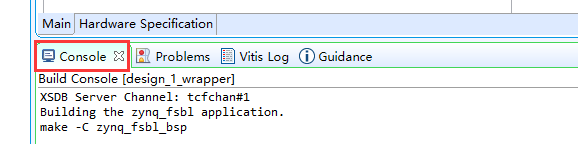

14)可以在Console看到编译过程

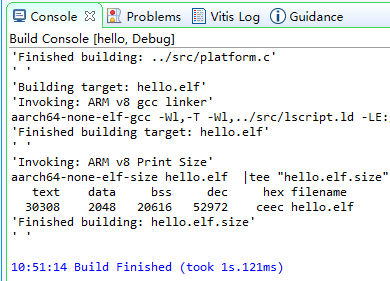

编译结束,生成elf文件

15)连接JTAG线到开发板、UART的USB线到PC

16)使用PuTTY软件做为串口终端调试工具,PuTTY是一个免安装的小软件

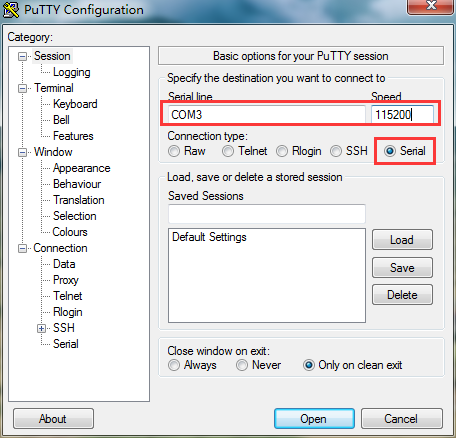

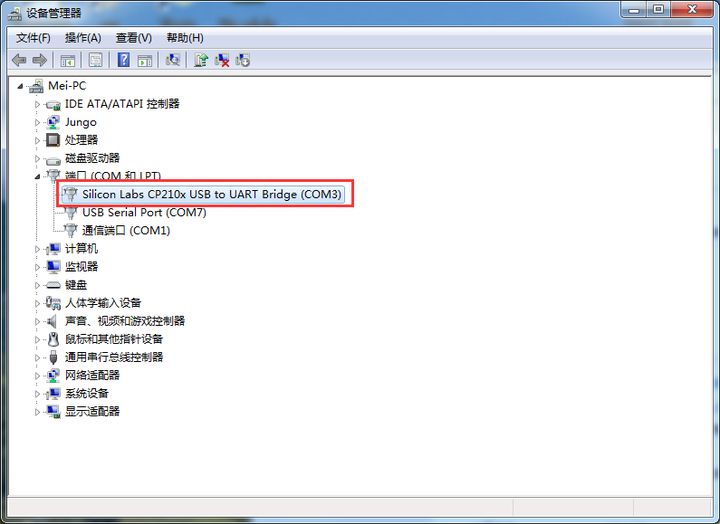

17)选择Serial,Serial line填写COM3,Speed填写115200,COM3串口号根据设备管理器里显示的填写,点击“Open”

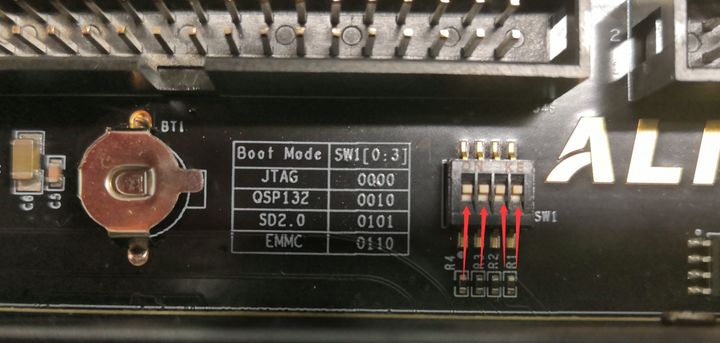

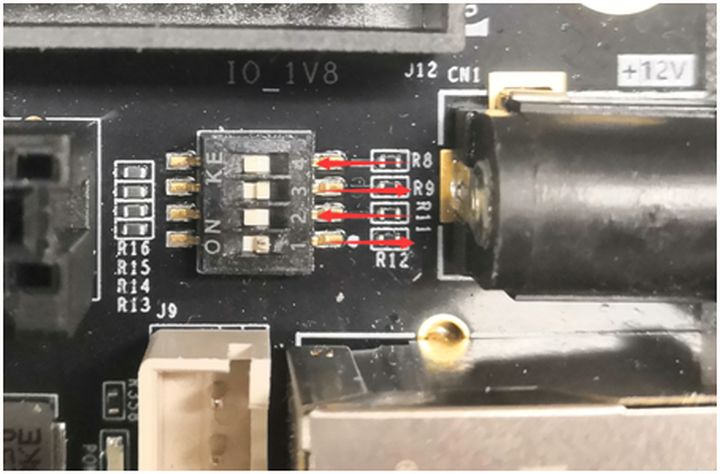

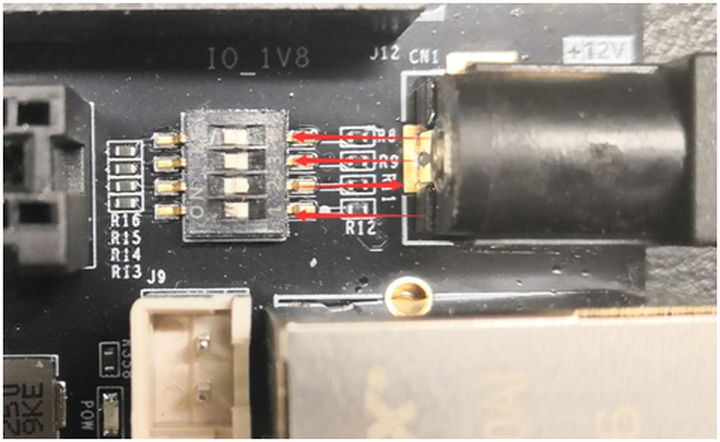

18)在上电之前最好将开发板的启动模式设置到JTAG模式,拔到”ON”的位置

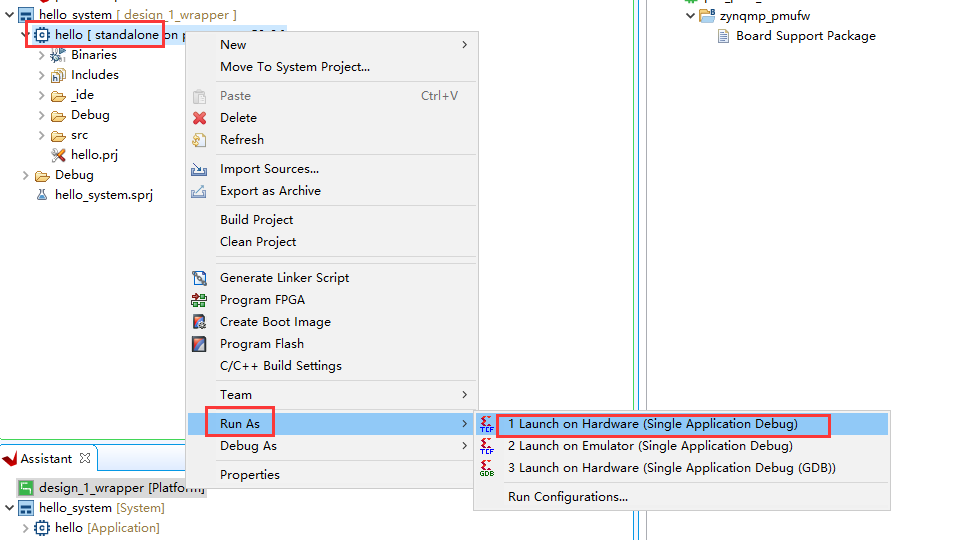

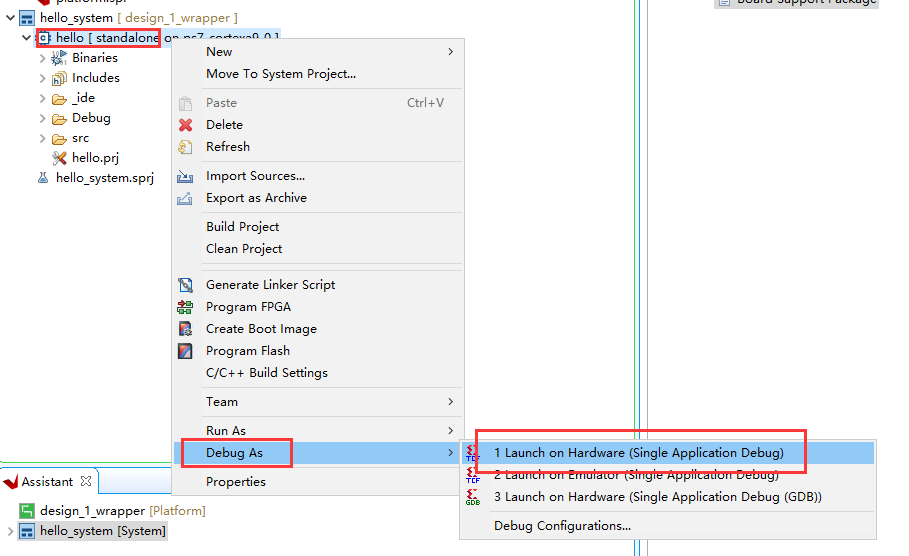

19)给开发板上电,准备运行程序,开发板出厂时带有程序,这里可以把运行模式选择JTAG模式,然后重新上电。选择“hello”,右键,可以看到很多选项,本实验要用到这里的“Run as”,就是把程序运行起来,“Run as”里又有很对选项,选择第一个“Launch on Hardware(Single Application Debug)”,使用系统调试,直接运行程序。

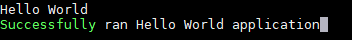

20)这个时候观察串口软件,即可以看到输出”Hello World”

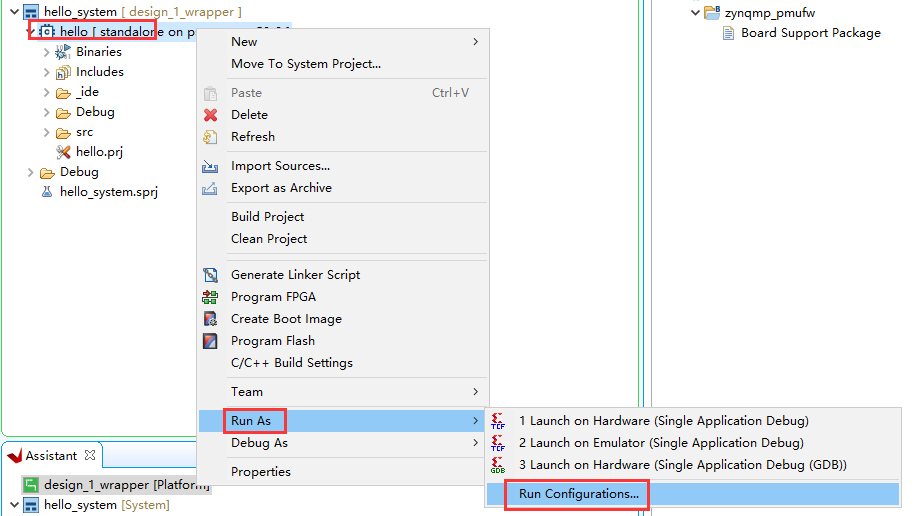

21)为了保证系统的可靠调试,最好是右键“Run As -> Run Configuration...”

22)我们可以看一下里面的配置,其中Reset entire system是默认选中的,这是跟以前的SDK软件不同的。如果系统中还有PL设计,还必须选择“Program FPGA”。

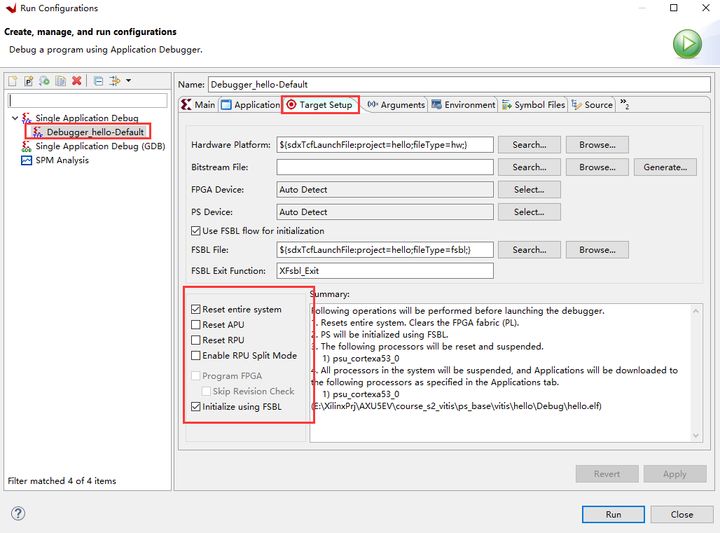

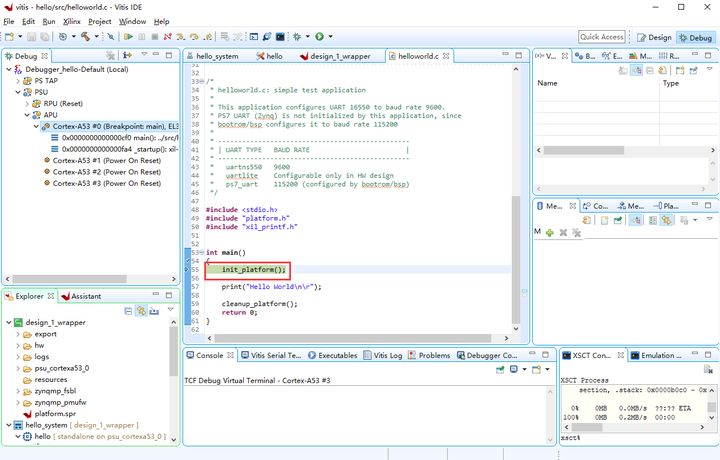

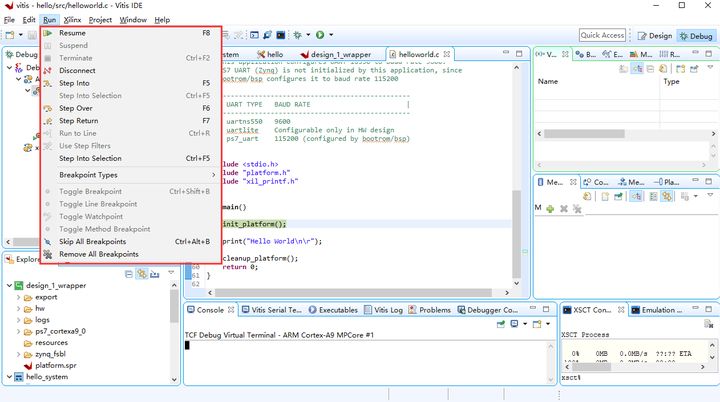

23)除了“Run As”,还可以“Debug As”,这样可以设置断点,单步运行

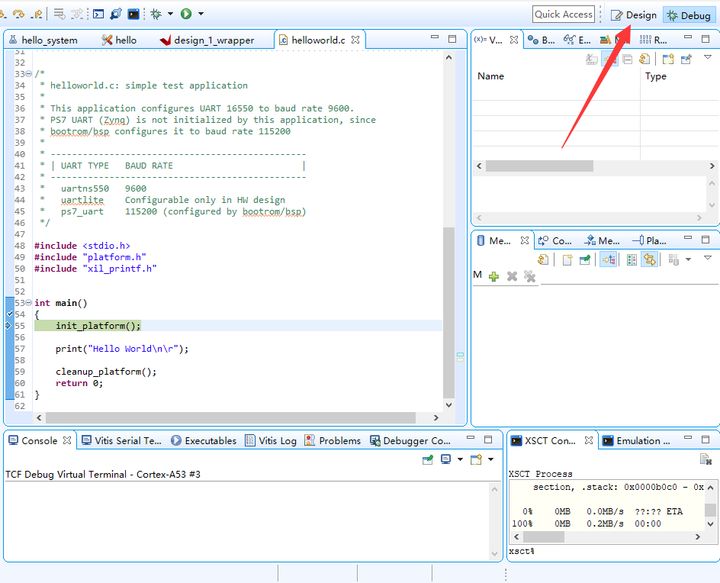

24)进入Debug模式

25)和其他C语言开发IDE一样,可以逐步运行、设置断点等

26)右上角可以切换IDE模式

3. 固化程序

普通的FPGA一般是可以从flash启动,或者被动加载,ZYNQ的启动是由ARM主导的,包括FPGA程序的加载,ZYNQ MPSoC启动一般为三个步骤,在UG1085中也有介绍:

Pre-configuration satge :预加载阶段由PMU控制,执行PMU ROM中的代码设置系统。PMU处理所有的复位和唤醒过程。

Configuration stage : 接下来进入最重要的一步,当BootRom(CSU ROM代码的一部分)搬运FSBL到OCM后,处理器开始执行FSBL代码,FSBL主要有以下几个作用:

Post-configuration stage : FSBL开始执行后,CSU ROM代码进入post-configuration阶段,负责起系统干预响应,CSU为验证文件正确性、通过PCAP加载PL、存储管理安全密钥、解密等提供持续的硬件支持。

3.1 生成FSBL

FSBL是一个二级引导程序,完成MIO的分配、时钟、PLL、DDR控制器初始化、SD、QSPI控制器初始化,通过启动模式查找bitstream配置FPGA,然后搜索用户程序加载到DDR,最后交接给应用程序执行。

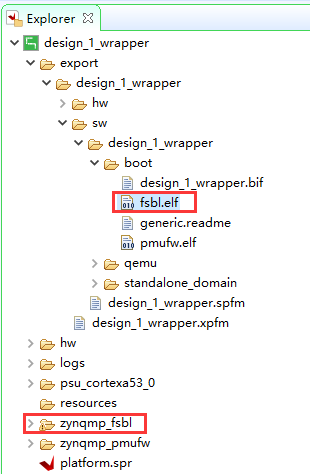

1) 由于在新建时选择了Generate boot components选项,所以Platform已经导入了fsbl的工程,并生成了相应的elf文件。

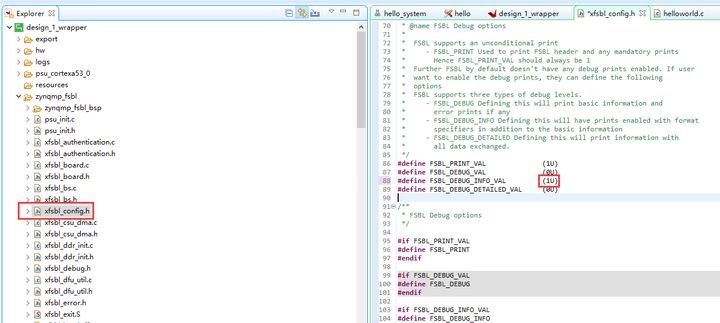

2) 修改调试宏定义FSBL_DEBUG_INFO_VAL,可以在启动输出FSBL的一些状态信息,有利于调试,但是会导致启动时间变长。保存文件。可以看一下fsbl里包含了很多外设的文件,包括psu_init.c,qspi,sd等,大家可以再仔细读读代码。当然这个fsbl模板也是可以修改的,至于怎么修改根据自己的需求来做。

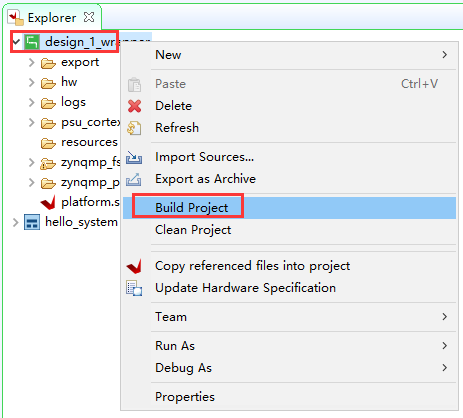

3) 重新Build Project

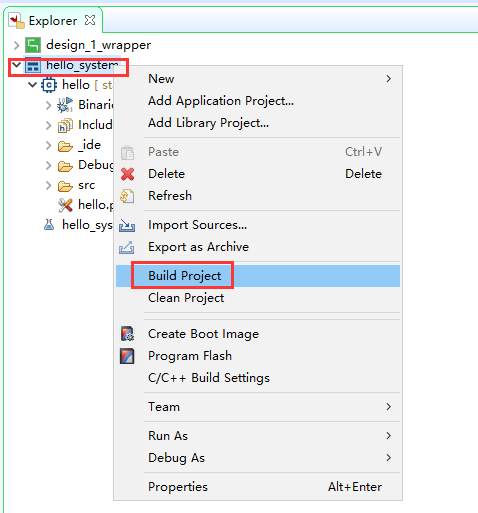

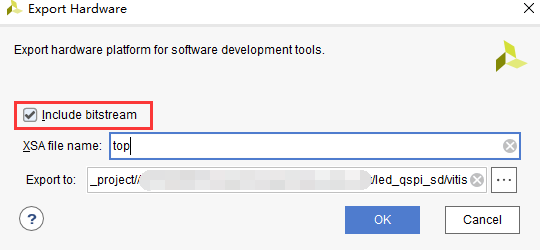

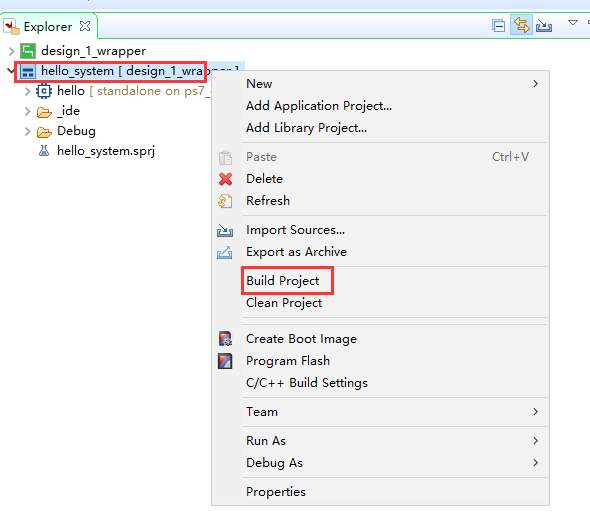

4) 接下来我们可以点击APP工程的system,右键选择Build project

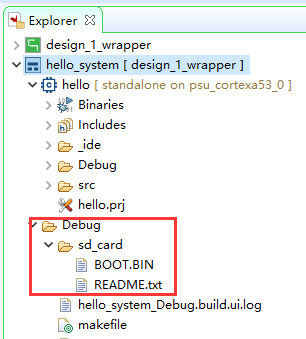

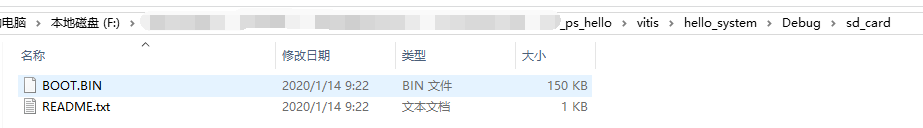

5) 这个时候就会多出一个Debug文件夹,生成了对应的BOOT.BIN

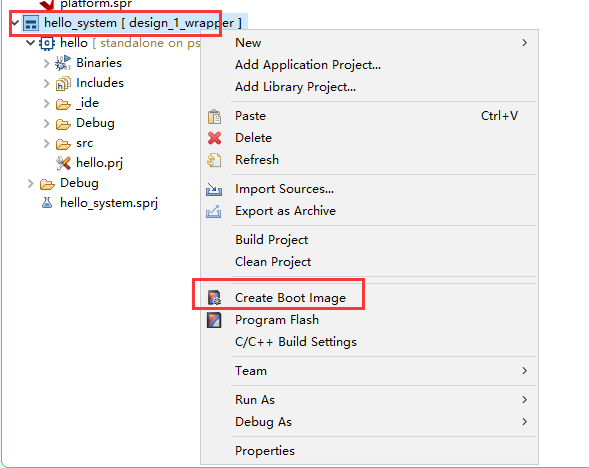

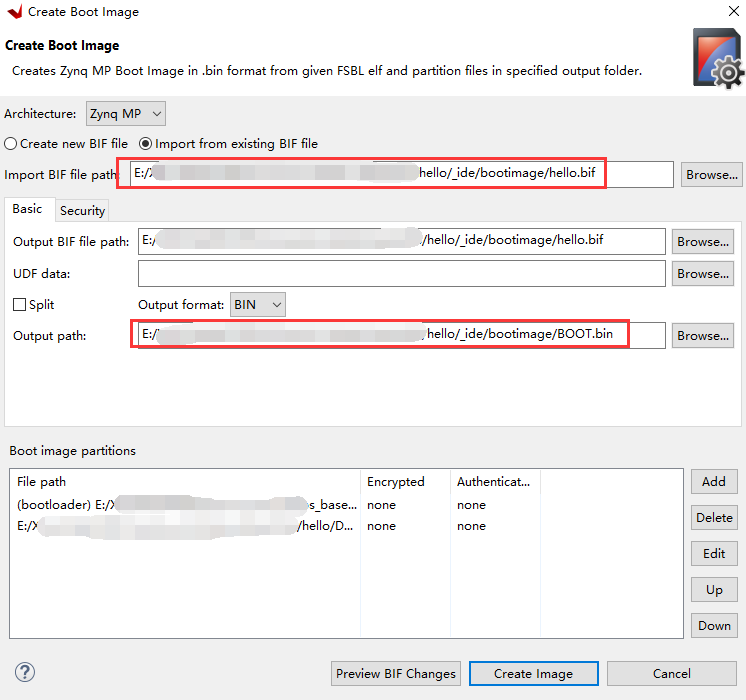

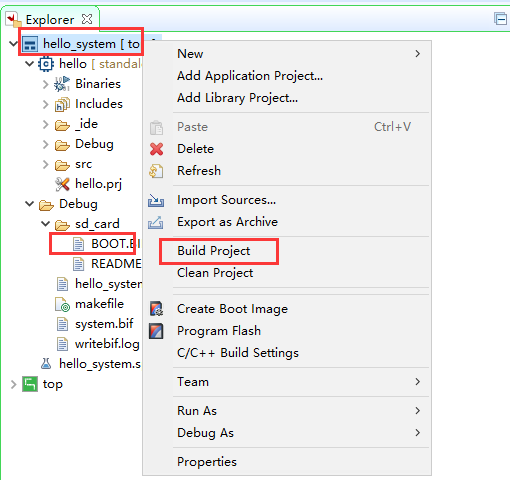

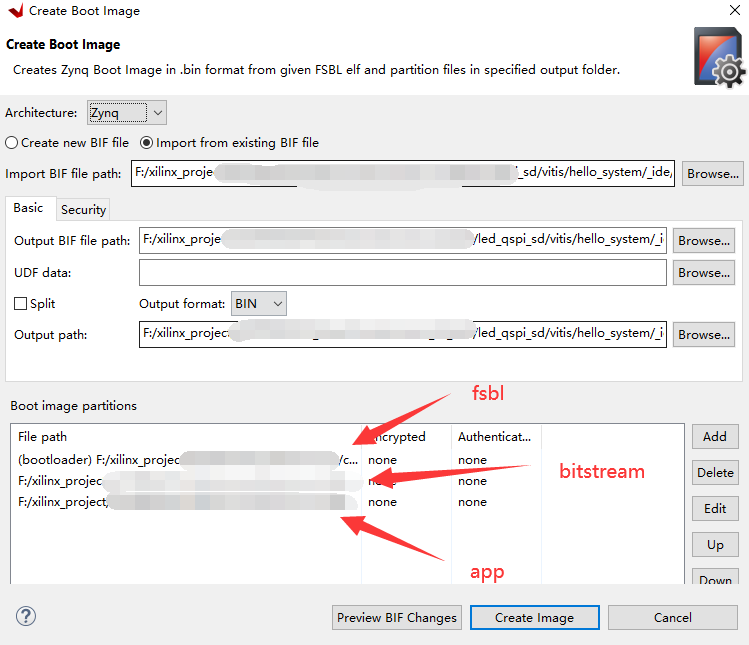

6) 还有一种方法就是,点击APP工程的system右键选择Creat Boot Image,弹出的窗口中可以看到生成的BIF文件路径,BIF文件是生成BOOT文件的配置文件,还有生成的BOOT.bin文件路径,BOOT.bin文件是我们需要的启动文件,可以放到SD卡启动,也可以烧写到QSPI Flash。

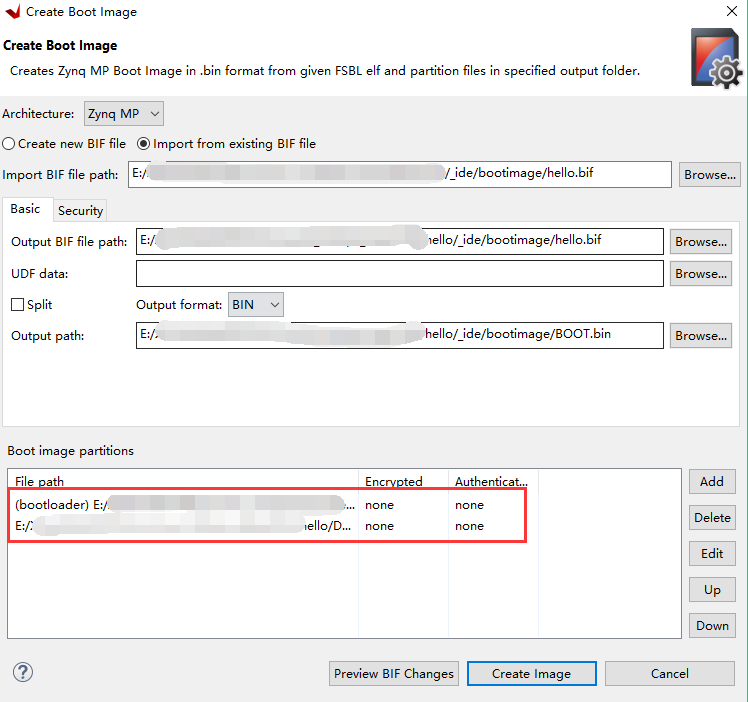

7) 在Boot image partitions列表中有要合成的文件,第一个文件一定是bootloader文件,就是上面生成的fsbl.elf文件,第二个文件是FPGA配置文件bitstream,在本实验中由于没有FPGA的bitstream,不需要添加,第三个是应用程序,在本实验中为hello.elf,由于没有bitstream,在本实验中只添加bootloader和应用程序。点击Create Image生成。

8) 在生成的目录下可以找到BOOT.bin文件

3.2 SD卡启动测试

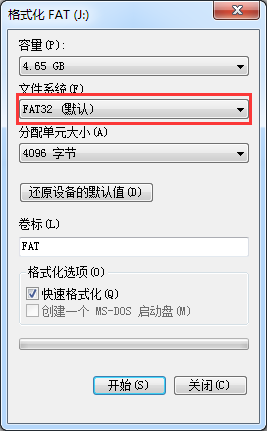

1) 格式化SD卡,只能格式化为FAT32格式,其他格式无法启动

2) 放入BOOT.bin文件,放在根目录

3) SD卡插入开发板的SD卡插槽

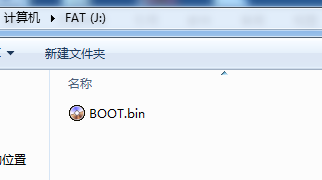

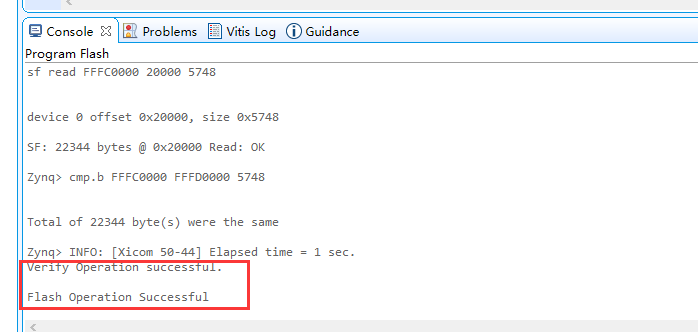

4) 启动模式调整为SD卡启动

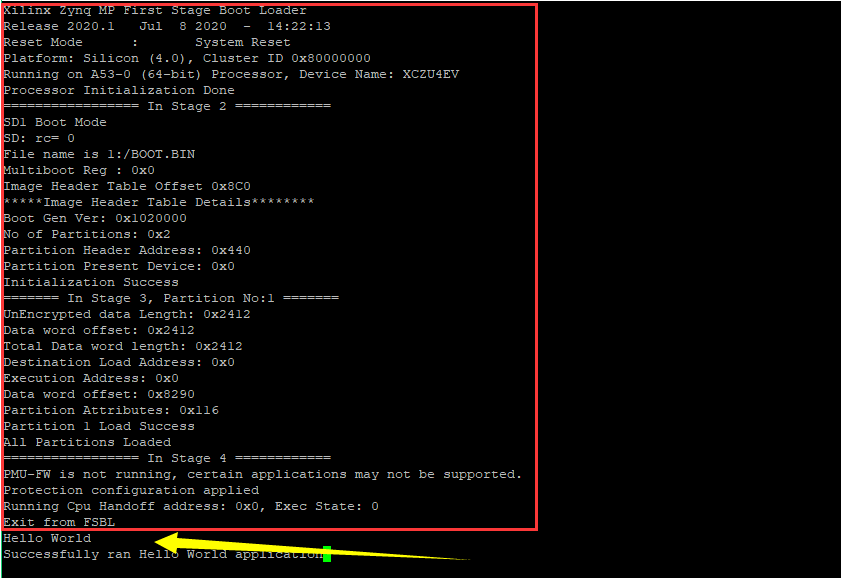

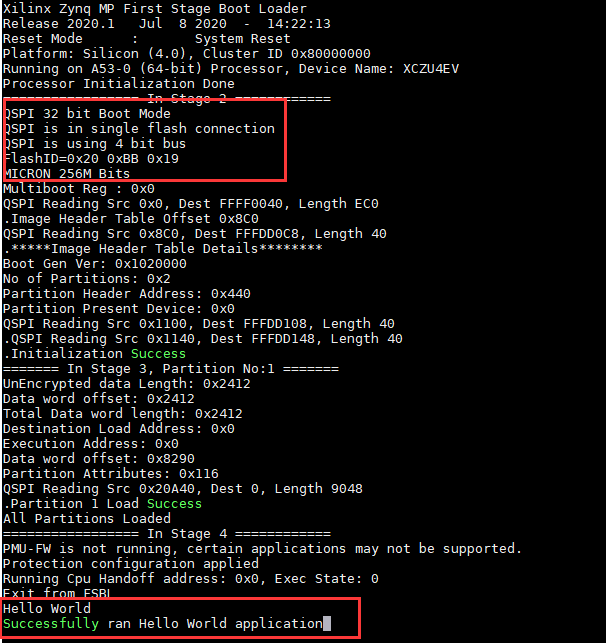

5) 打开串口软件,上电启动,即可看到打印信息,红色框为FSBL启动信息,黄色箭头部分为执行的应用程序helloworld

3.3 QSPI启动测试

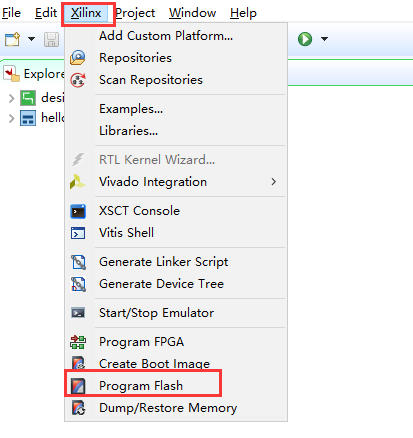

1) 在Vitis菜单Xilinx -> Program Flash

2) Hardware Platform选择最新的,Image FIle文件选择要烧写的BOOT.bin,FSBL file选择fsbl.elf。选择Verify after flash,在烧写完成后校验flash。

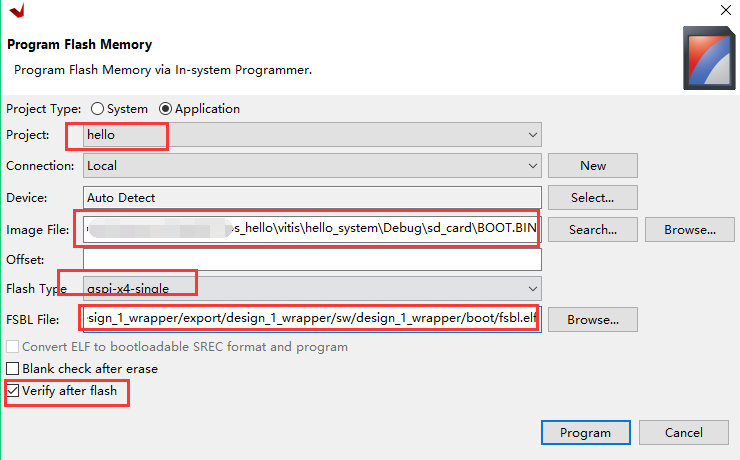

3) 点击Program等待烧写完成

4) 设置启动模式为QSPI,再次启动,可以在串口软件里看到与SD同样的启动效果。

3.4 Vivado下烧写QSPI

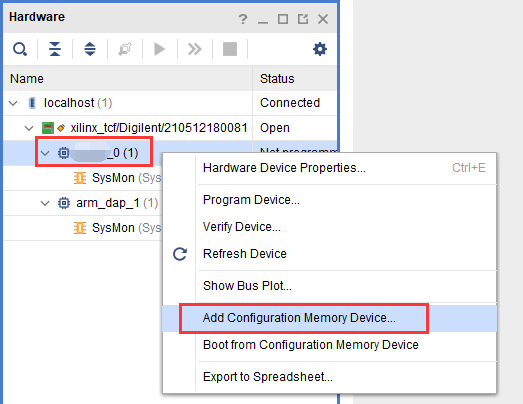

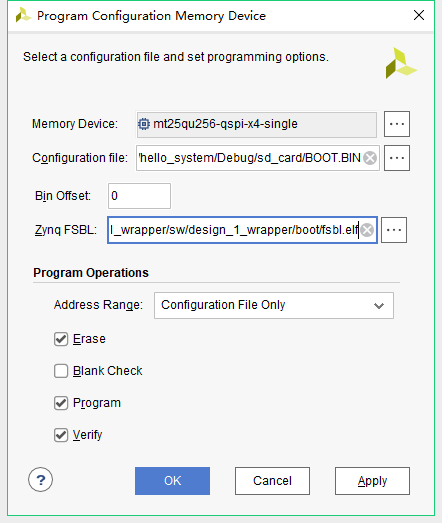

1) 在HARDWARE MANGER下选择器件,右键Add Configuration Memory Device

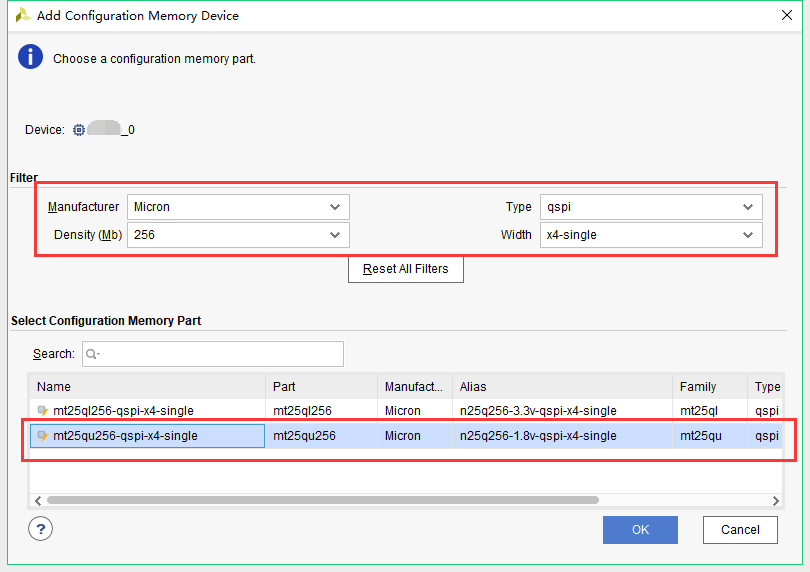

2) 选择尝试Micron,类型选择qspi,宽度选择x4-single,Density选择256,这时候出现wt25qu256,选择红框型号。

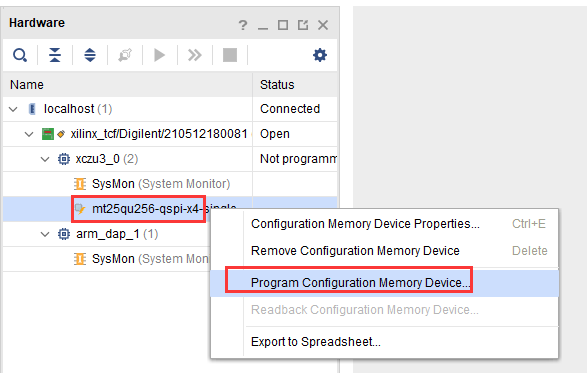

3) 右键选择编程文件

4) 选择要烧写的文件和fsbl文件,就可以烧写了,如果烧写时不是JTAG启动模式,软件会给出一个警告,所以建议烧写QSPI的时候设置到JTAG启动模式

3.5 使用批处理文件快速烧写QSPI

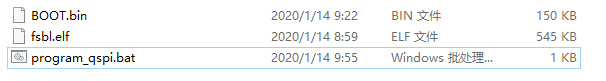

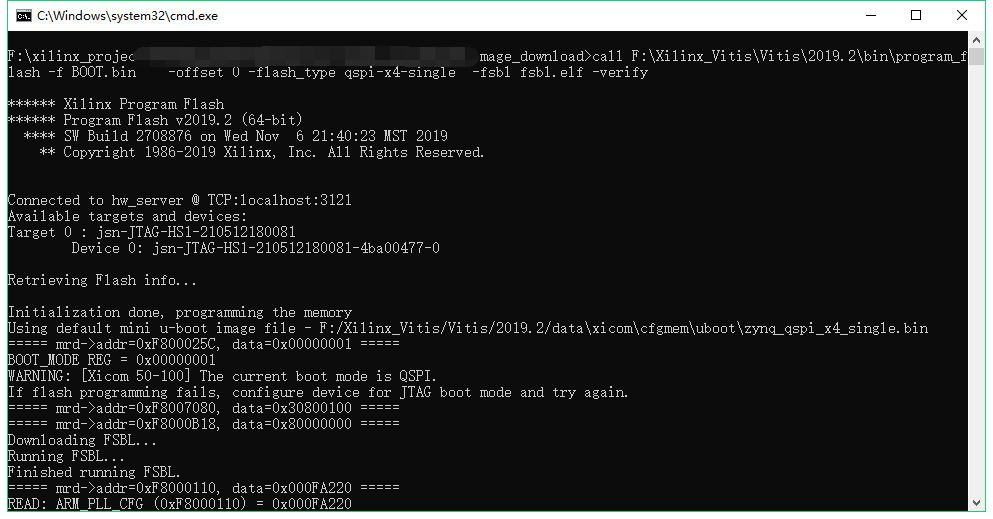

1) 新建一个program_qspi.txt文本文件,扩展名改为bat,内容填写如下,

E:/XilinxVitis/Vitis/2020.1/bin/program_flash 为我们工具路径,按照安装路径适当修改,-f 为要烧写的文件,-fsbl为要烧写使用的fsbl文件,-verify为校验选项。

callE:/XilinxVitis/Vitis/2020.1/bin/program_flash -f BOOT.bin -offset 0 -flash_type qspi-x4-single -fsbl fsbl.elf -verifypause

2) 把要烧录的BOOT.bin、fsbl、bat文件放在一起

3) 插上JTAG线后上电,双击bat文件即可烧写flash。

4. 常见问题

4.1 仅有PL端逻辑的固化

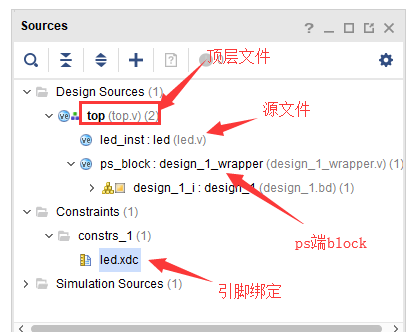

有很多人会问,如果只有PL端的逻辑,不需要PS端该怎么固化程序呢?不带ARM的FPGA固化是没问题的,但是对于ZYNQ来说,必须要有PS端的配合才能固化程序。那么对于前面的”PL的“Hello World”LED实验”该怎么固化程序呢?

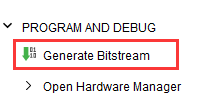

1) 根据本章的PS端添加ZYNQ核并配置,最简单的方法就是在本章工程的基础上添加LED实验的verilog源文件,并进行例化,组成一个系统,并需要生成bitstream。

2) 生成bitstream之后,导出硬件,选择include bitstream

3) 在生成BOOT.BIN时,还是需要一个app工程hello,仅仅是为了生成BOOT.BIN,默认情况下在system右键Build Project,即可生成包含bitstream的BOOT.BIN。

打开Create Boot Image界面可以看到,Boot Image Partitions的文件顺序是fsbl、bitstream、app,注意顺序不要颠倒,利用这样生成的BOOT.BIN就可以按照前面的启动方式测试启动了

在course_s2文件夹,我们提供了一个名为led_qspi_sd的工程,大家可以参考。

5. 使用技巧分享

在频繁的修改源文件,并进行编译的时候,最好选择APP工程进行Build Project,这种情况下只会生成elf文件。

如果想生成BOOT.BIN文件,可以选择system进行编译,这种情况既会生成elf也会生成BOOT.BIN,笔者最开始用的时候就吃过亏,每次编译都是选择system,结果每次都要等待生成BOOT.BIN,浪费时间,大家可以注意一下。

6. 本章小结

本章从FPGA工程师和软件工程师两者角度出发,介绍了ZYNQ开发的经典流程,FPGA工程师的主要工作是搭建好硬件平台,提供硬件描述文件hdf给软件工程师,软件工程师在此基础上开发应用程序。本章是一个简单的例子介绍了FPGA和软件工程师协同工作,后续还会牵涉到PS与PL之间的联合调试,较为复杂,也是ZYNQ开发的核心部分。

同时也介绍了FSBL,启动文件的制作,SD卡启动方式,QSPI下载及启动方式,Vivado下载BOOT.BIN方式,本章没有FPGA加载文件,后面的应用中会再介绍添加FPGA加载文件制作BOOT.BIN。

后续的工程都会以本章节的配置为准,后面不再介绍ZYNQ的基本配置。

千里之行,始于足下,相信经过本章的学习,大家对ZYNQ开发有了基本概念,高楼稳不稳,要看地基打的牢不牢,虽然本章较为简单,但也有很多知识点待诸位慢慢消化。加油!!!

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章