资料下载

×

如何使用FPGA实现运动估计算法的设计

消耗积分:0 |

格式:rar |

大小:0.49 MB |

2021-02-03

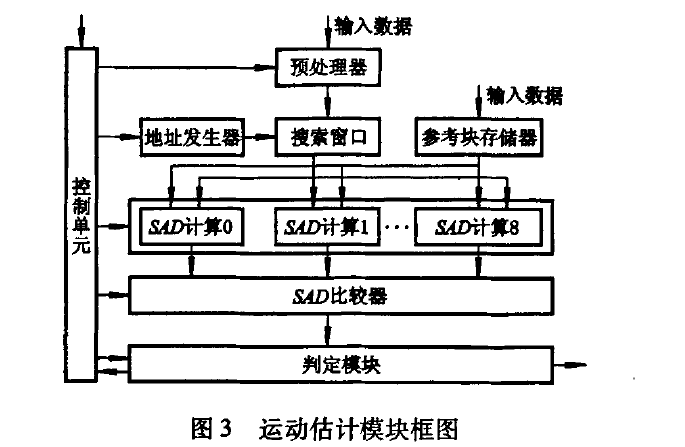

为进一步提高编码效率,在研究菱形算法的基础上,采用了“十字”形运动估计算法,设计了硬件电路,并用H‘GA(Field-Pmg隐mmable Gate Amy)实现了算法.结合算法的特点,设计了整体框架结构,提出了一种高度并行、紧凑流水线的FPGA实现方案.用Verilog HDL硬件描述语言设计了编码,在QuARTuSⅡ集成开发环境下,进行了仿真验证,并写入FPGA芯片,实现了“十字”形运动估计算法.经测试表明:该设计方案搜索高效、逻辑简洁,对比全搜索法占用硬件资源较小.可广泛应用到移动视频通信、远程无线监控等领域.

运动估计是视频压缩中的关键环节,被广泛应用于视频编码标准中(如MPEG4).块匹配算法是目前应用最广泛的运动估计算法.其中全搜索算法精度最高,但计算过于复杂,不宜在实时环境中使用.因此,提出了很多快速算法,如T.Koga等提出的三步法¨3和J.R.Jain等提出的二维对数法,由于限制了搜索位的数目,不利于估计小的运动且容易陷入局部最小.接着R.U等提出的新三步法、L.M.Po等提出的四步法、L.K.uu等提出的梯度下降法等,虽然提高了速度,但逻辑复杂,不利于硬件实现.后来S.zhu等提出的菱形算法‘21,搜索更加高效,但也同样存在硬件实现时逻辑复杂.笔者通过改变菱形算法,提出一种有利于硬件实现的运动估计算法,并进一步研究采用FPGA实现的方法.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章