资料下载

RS232串口通信接收接口的毕业设计论文

目前,随着集成电路集成度的增加,电子计算机向微型化和超微型化方向发展,微型计算机已成为导弹,智能机器人,人类宇宙和太空和太空奥妙复杂系统不可缺少的智能部件。在一些工业控制中,经常需要以多台单片机作为下位机执行对被控对象的直接控制,以一台PC机为上位机完成复杂的数据处理,组成一种以集中管理、分散控制为特点的集散控制系统。

串口是计算机上一种非常通用的设备通讯协议,大多数计算机包容两个基于RS232的串口。串口同时也是仪器仪表设备通过用的通讯协议,很多GPIB兼容的设备也带有RS-232口。同时串口通讯协议也可以用于获取远程采集设备数据。所以,深入的理解学习和研究串口通信相关知识是非常必要的。此次数字系统课程设计选题为“串行通信接收接口(数码管)”,使用DE2开发板来实现一个主从式的总线通讯系统,即实现PC机与DE2的数据接收,并在数码管上显示。通过此次设计,对串口通讯的原理和应用融会贯通,为以后的时间工作储备知识和研究打下基础。

串行通信接收接口(数码管)

基本要求:掌握RS232串口的协议,运用DE2的串口进行接收PC的数据。波特率为9600,8位数据位,无奇偶校验,一个停止位。

硬件验证要求:在PC机通过“串行通信调试助手”软件发送数据,DE2通过串口接收数据,完成接收数据后在数码管上面进行显示。

首先,对课设选题的分析与方法选择:串行通信中,线路空闲时,线路的TTL电平总是高,经反串行通信中,线路空闲时,线路的TTL电平总是高,经反向RS232的电平总是低。一个数据的开始RS232线路为高电平,结束时RS232为低电平。数据总是从低位向高位一位一位的传输。示波器读数时,左边是数据的低位。由此进行数据的输送。

课程设计的目的:

学习RS-232串口通信数据结构,并编程完成串行数据的接收和显示。

掌握RS-232的工作机制与原理。

熟练掌握Quartus2软件的使用。

了解CPLD/FPGA实验箱。

2.课程设计题目描述和要求:

(1)课程设计题目:基于FPGA的串口通信程序设计。

(2)课程设计要求:

下述设计内容需由学生个人独立完成:

1.理解电路原理图与工作过程;

2.掌握RS-232电气特性;

3.掌握RS-232通信原理及串口通信数据格式,并编程完成串行数据的接收和显示;

4.能正确处理编程与调试过程中所遇到的问题;

5. 在FPGA中构造一个异步串行通信控制模块,完成PC机发送的接收,并设计显示模块,完成接收数据的显示

(3)要求的设计成果:

掌握RS232串口的协议,运用DE2的串口进行接收PC的数据。波特率为9600,8位数据位,无奇偶校验,一个停止位。

硬件验证要求:在PC机通过“串行通信调试助手”软件发送数据,DE2通过串口接收数据,完成接收数据后在数码管上面进行显示。

课程设计报告内容:

3.1课程设计方案及基本原理:

1、Verilog简介

Verilog是一种流行的硬件描述语言,他是由工业界开发的,1984年,Verilog作为一种私用的硬件描述语言,由Gateway Design Automation公司给出,1988年,Synopsis公司为Verilog开发了综合工具。1995年,Verilog成为IEEE的一个标准。Verilog 适合算法级,寄存器级,逻辑级,门级和版图级等各个层次的设计和描述。

Verilog的语法是基于C语言的。由于是基于C语言,所以它更容易掌握。本设计中采用Verilog语言进行设计。

2、设计工具简介

本次设计是基于Altera公司的QuartusII软件。

Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

QuartusII支持Altera的IP核,包含了LPM/MegaFuction宏功能模块库,使用它,可以简化设计的复杂性,加快设计速度。QuartusII平台支持一个工作组环境下的设计要求,其中包括支持基于Internet的协作设计。此外,QuartusII通过和DSP Builder工具与Matlab/SIMULINK相结合,可以方便地实现各种DSP应用系统;支持Altera的片上可编程系统开发,集系统级设计、嵌入式软件设计、可编程逻辑设计于一体,是一种综性的开发平台。

3、设计方案:

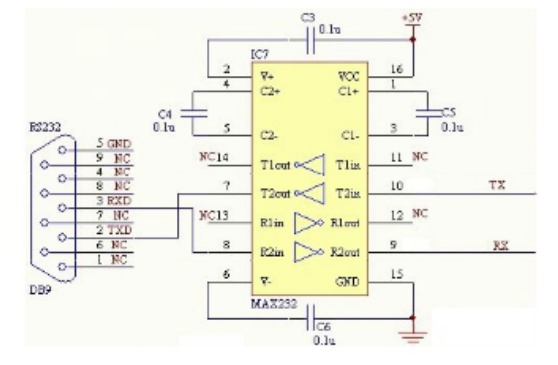

利用实验箱上的MAX232芯片控制通过适当分频(分频的目的是为了达到要求的波特率,控制数据传输速率)的串行输入信号,并将其转换为并行信号并通过实验箱上的数码管的后两位显示从计算机中传输出来的16进制数。例如在计算机端输入(FF)则会在试验箱上看到(000000FF)的显示图示。

4、基本原理:

RS-323C标准是美国EIA(电子工业联合会)与BELL等公司一起开发的1969年公布的通信协议。它适合于数据传输速率在0~20000b/s范围内的通信。这个标准对串行通信接口的有关问题,如信号线功能、电器特性都作了明确规定。

EIA-RS-232C中+3V~+15V之间的电平为‘0’,-3V~-15V的电平为‘1’;与TTL以高低电平表示逻辑状态的规定不同。因此,为了能够同计算机接口或终端的TTL器件连接,必须在EIA-RS-232C与TTL电路之间进行电平和逻辑关系的变换。实现这种变换的方法可用分立元件,也可用集成电路芯片。目前较为广泛地使用集成电路转换器件,如MC1488、SN75150芯片可完成TTL电平到EIA电平的转换,而MC1489、SN75154可实现EIA电平到TTL电平的转换。MAX232芯片可完成TTL←→EIA双向电平转换。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章