资料下载

×

从零开始写RISC-V处理器

消耗积分:0 |

格式:rar |

大小:5.43 MB |

2022-03-17

1、初衷

本开源项目的初衷是本人想入门RISC-V,熟悉RISC-V的指令内容和汇编语法。

本人对RISC-V很感兴趣,很看好RISC-V的发展前景,觉得RISC-V就是CPU中的Linux。由于RISC-V是这两年才开始迅速发展的,因此关于RISC-V的学习参考资料目前还很少,特别是适合入门的资料,因此学习起来进度很缓慢,于是萌生了自己从零开始写RISC-V处理器核的想法。

本人是一名FPGA小白,为了快速入门、深入掌握RISC-V,我开始了学习FPGA和verilog的"艰难"历程。我工作的内容是和嵌入式软件相关的,平时根本不会接触到FPGA,也不会用到RISC-V,因此只能用业余时间来学习RISC-V。

网上有不少关于RISC-V的开源项目,但是大多都写得很"高深",对于我这种小白来说学习起来是非常吃力的,不太适合入门。本项目目前的代码量非常少,是很简单易懂的,对于想入门RISC-V的同学来说是一个很好的参考,希望能够吸引更多的同学参与到RISC-V的学习中来,促进RISC-V的发展,如果能起到抛砖引玉的作用的话那就更好了,也许说是砖的话就有点夸大了,但哪怕是起到一颗沙子的作用,也就足矣。

2、介绍

本项目实现的是一个单核32位的小型RISC-V处理器核(tinyriscv),采用verilog语言编写。设计目标是对标ARM Cortex-M3系列处理器。tinyriscv有以下特点:

rtl:该目录包含tinyriscv的所有verilog源码;

sim:该目录包含仿真批处理bat文件和脚本;

tests:该目录包含测试程序源码,其中example目录为C语言程序例程源码,isa目录为RV32指令测试源码;

tools:该目录包含编译汇编和C语言程序所需GNU工具链和将二进制文件转成仿真所需的mem格式文件的脚本,还有通过串口下载程序的脚本。

pic:存放图片;

tb:该目录包含仿真的testbench文件;

fpga:存放FPGA相关文件,比如约束文件;

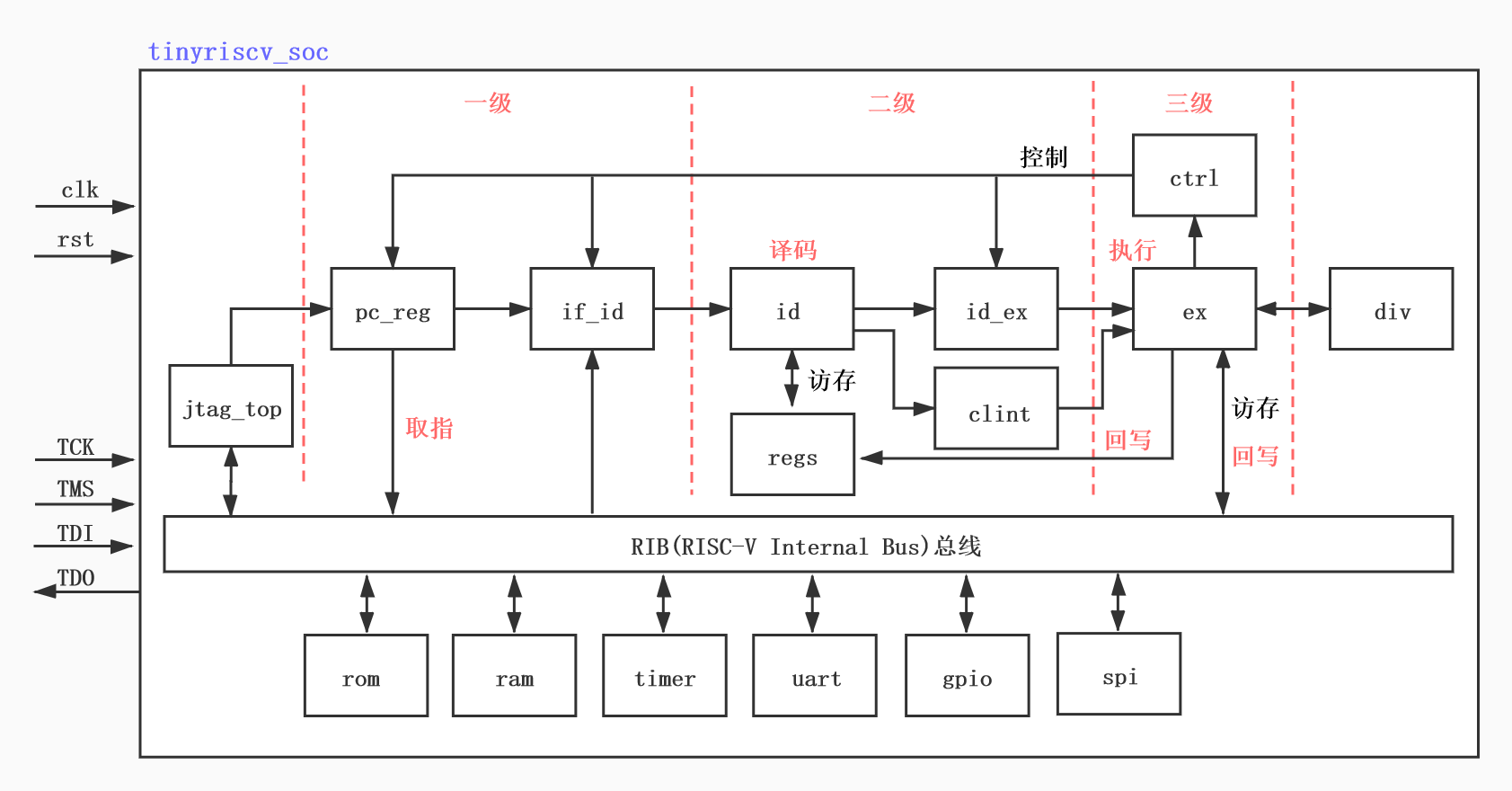

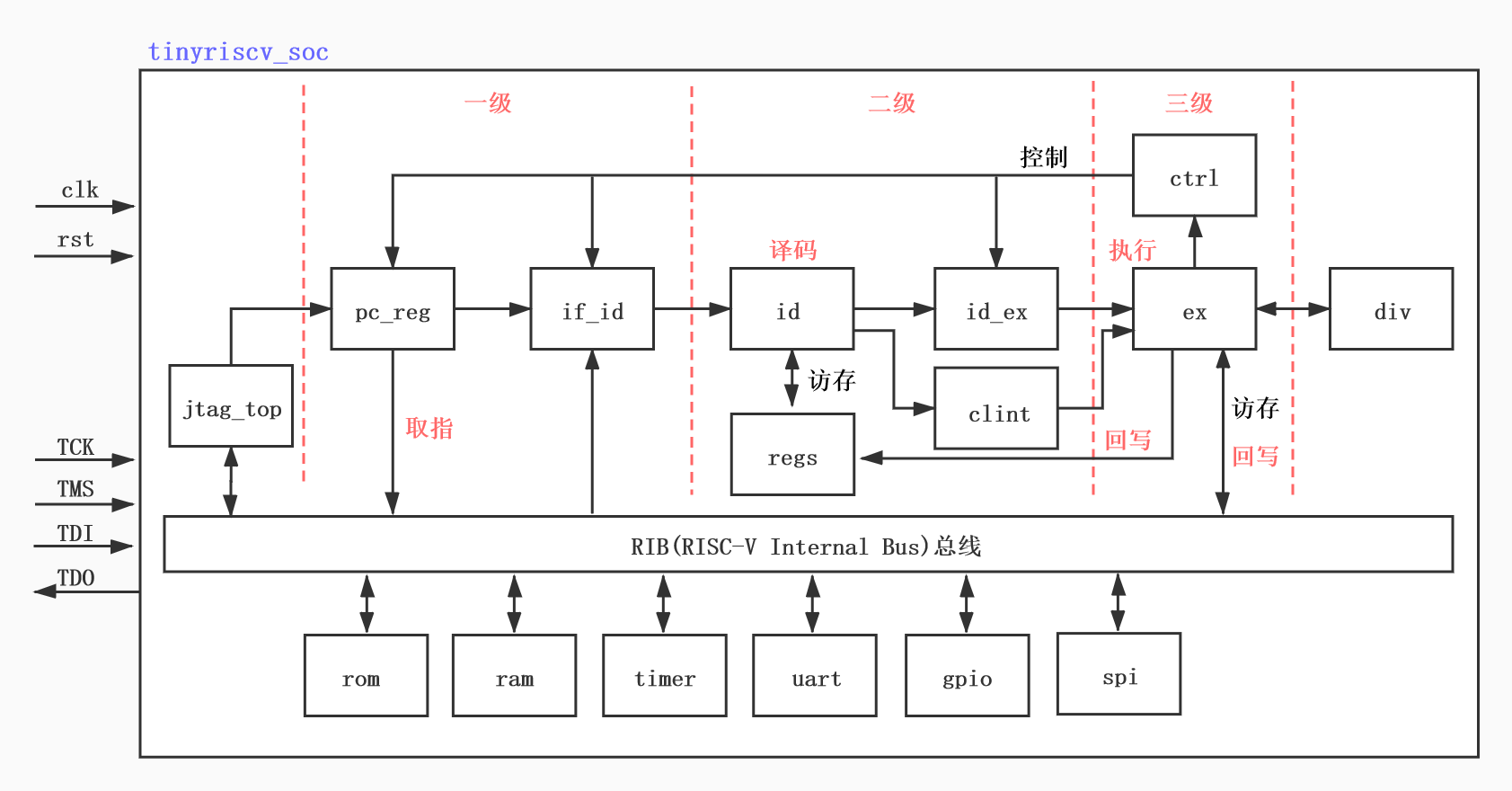

tinyriscv的整体框架如下:

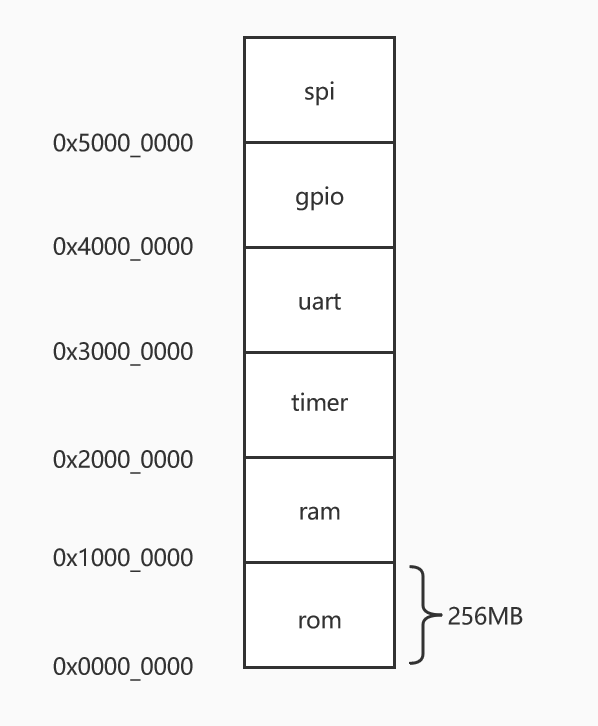

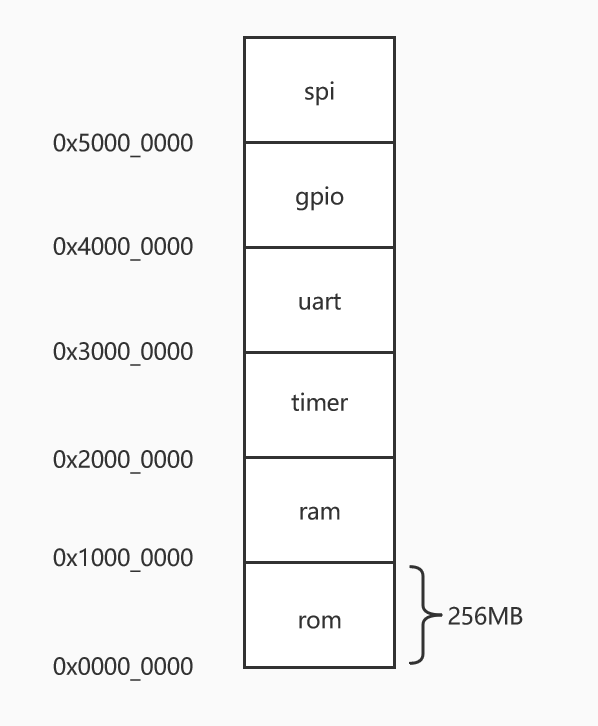

tinyriscv目前外挂了6个外设,每个外设的空间大小为256MB,地址空间分配如下图所示:

3、CoreMark测试

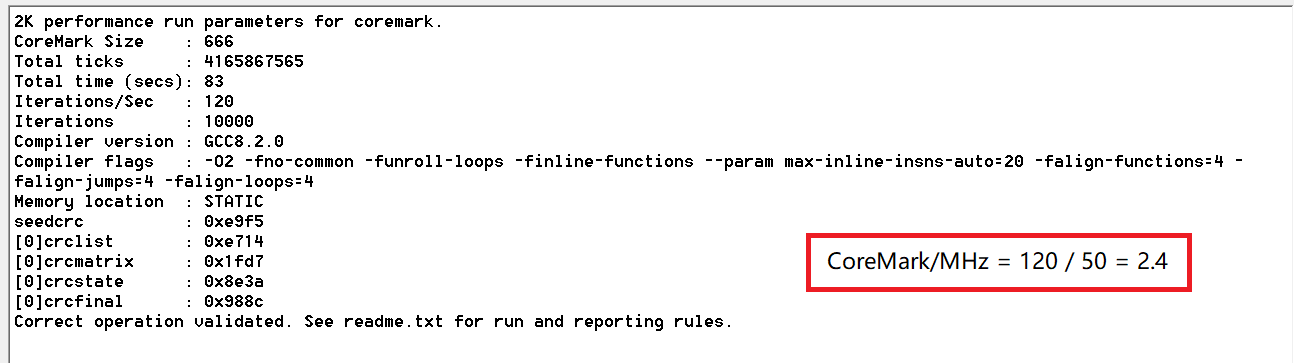

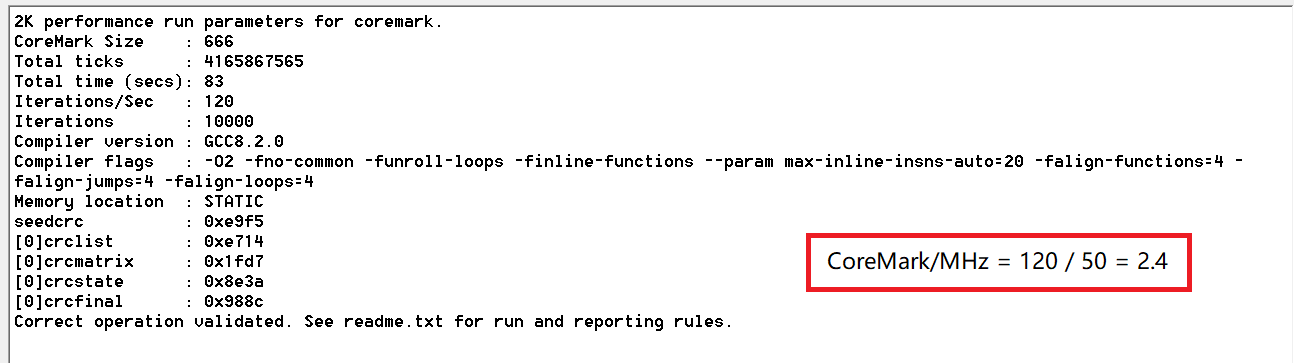

目前tinyriscv在Xilinx Artix-7 35T FPGA平台(时钟50MHz)上运行CoreMark跑分程序的结果如下图所示:

可知,tinyriscv的跑分成绩为2.4。

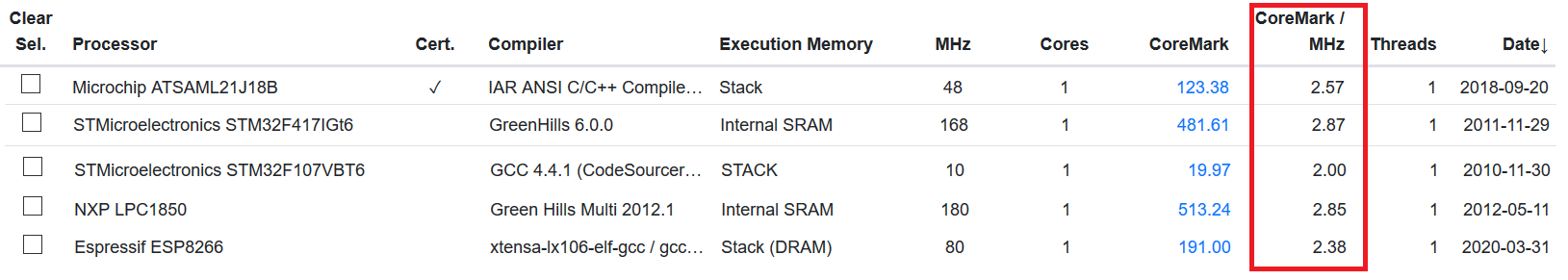

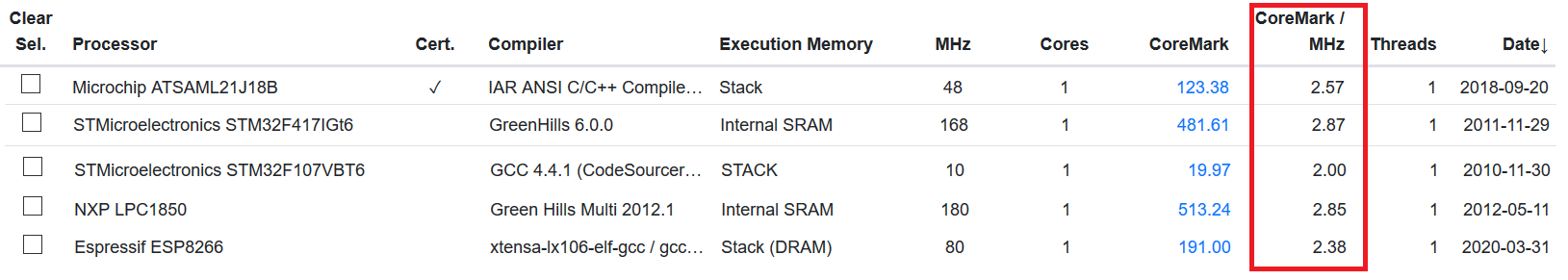

选了几款其他MCU的跑分结果如下图所示:

更多MCU的跑分结果,可以到coremark官网查询。

4、如何使用

本项目可以运行在Windows和Linux平台(macOS平台理论上也是可以的),编译仿真工具使用的是iverilog和vpp,波形查看工具使用的是gtkwave。

4.1Windows平台环境搭建

使用之前需要安装一下工具

1.安装iverilog工具

可以在上面进行下载,安装过程中记得同意把iverilog添加到环境变量中,当然也可以在安装完成后手动进行添加。安装完成后iverilog、vvp和gtkwave等工具也就安装好了。

2.安装GNU工具链

下载完成后将压缩包解压到本项目的tools目录下。注意目录的层次结构,解压后的工具路径应该如下所示:

3.安装make工具

下载完成后直接解压,然后将make所在的路径添加到环境变量里。

4.安装python3

到python官网下载win版本的python,注意要下载python3版本的。安装完后将python添加到环境变量里。

5.下载tinyriscv代码

使用git clone命令下载,不要使用zip方式下载,否则有些文件会有格式问题。

本开源项目的初衷是本人想入门RISC-V,熟悉RISC-V的指令内容和汇编语法。

本人对RISC-V很感兴趣,很看好RISC-V的发展前景,觉得RISC-V就是CPU中的Linux。由于RISC-V是这两年才开始迅速发展的,因此关于RISC-V的学习参考资料目前还很少,特别是适合入门的资料,因此学习起来进度很缓慢,于是萌生了自己从零开始写RISC-V处理器核的想法。

本人是一名FPGA小白,为了快速入门、深入掌握RISC-V,我开始了学习FPGA和verilog的"艰难"历程。我工作的内容是和嵌入式软件相关的,平时根本不会接触到FPGA,也不会用到RISC-V,因此只能用业余时间来学习RISC-V。

网上有不少关于RISC-V的开源项目,但是大多都写得很"高深",对于我这种小白来说学习起来是非常吃力的,不太适合入门。本项目目前的代码量非常少,是很简单易懂的,对于想入门RISC-V的同学来说是一个很好的参考,希望能够吸引更多的同学参与到RISC-V的学习中来,促进RISC-V的发展,如果能起到抛砖引玉的作用的话那就更好了,也许说是砖的话就有点夸大了,但哪怕是起到一颗沙子的作用,也就足矣。

2、介绍

本项目实现的是一个单核32位的小型RISC-V处理器核(tinyriscv),采用verilog语言编写。设计目标是对标ARM Cortex-M3系列处理器。tinyriscv有以下特点:

- 支持RV32IM指令集,通过RISC-V指令兼容性测试;

- 采用三级流水线,即取指,译码,执行;

- 可以运行C语言程序;

- 支持JTAG,可以通过openocd读写内存(在线更新程序);

- 支持中断;

- 支持总线;

- 支持FreeRTOS;

- 支持通过串口更新程序;

- 容易移植到任何FPGA平台(如果资源足够的话);

- 项目中的各目录说明:

rtl:该目录包含tinyriscv的所有verilog源码;

sim:该目录包含仿真批处理bat文件和脚本;

tests:该目录包含测试程序源码,其中example目录为C语言程序例程源码,isa目录为RV32指令测试源码;

tools:该目录包含编译汇编和C语言程序所需GNU工具链和将二进制文件转成仿真所需的mem格式文件的脚本,还有通过串口下载程序的脚本。

pic:存放图片;

tb:该目录包含仿真的testbench文件;

fpga:存放FPGA相关文件,比如约束文件;

tinyriscv的整体框架如下:

tinyriscv目前外挂了6个外设,每个外设的空间大小为256MB,地址空间分配如下图所示:

3、CoreMark测试

目前tinyriscv在Xilinx Artix-7 35T FPGA平台(时钟50MHz)上运行CoreMark跑分程序的结果如下图所示:

可知,tinyriscv的跑分成绩为2.4。

选了几款其他MCU的跑分结果如下图所示:

更多MCU的跑分结果,可以到coremark官网查询。

4、如何使用

本项目可以运行在Windows和Linux平台(macOS平台理论上也是可以的),编译仿真工具使用的是iverilog和vpp,波形查看工具使用的是gtkwave。

4.1Windows平台环境搭建

使用之前需要安装一下工具

1.安装iverilog工具

可以在上面进行下载,安装过程中记得同意把iverilog添加到环境变量中,当然也可以在安装完成后手动进行添加。安装完成后iverilog、vvp和gtkwave等工具也就安装好了。

2.安装GNU工具链

下载完成后将压缩包解压到本项目的tools目录下。注意目录的层次结构,解压后的工具路径应该如下所示:

3.安装make工具

下载完成后直接解压,然后将make所在的路径添加到环境变量里。

4.安装python3

到python官网下载win版本的python,注意要下载python3版本的。安装完后将python添加到环境变量里。

5.下载tinyriscv代码

使用git clone命令下载,不要使用zip方式下载,否则有些文件会有格式问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章