资料下载

使用FPGA创建RISC V系统

描述

大家都知道现在的处理器是RISC-V,即使它本身不是处理器,基于 RISC-V 的板的数量也越来越多。要了解其中的原因,我们必须了解什么是 RISC-V,以及它与 Arm® 或 x86 的不同之处。首先我们要知道RISC-V不是处理器,像Arm或者x86,它们是指令集架构(ISA),特别是开放指令集架构,开放的字就大了RISC-V 和 Arm 或 x86 之间的区别。我将举例说明,如果我是一名 ASIC 设计师,并且我想在我的设计中集成一个处理器,我有两个选择,第一个也是迄今为止最常见的一个是支付给 Arm Limited,它的所有者是Arm Architecture,让我设计一个使用他们的架构的处理器,并符合他们的指令集。这将使我的设计到达大量的开发人员,他们的设计符合 Arm 架构。您拥有的第二个选项是设计符合 RISC-V 的处理器。在这种情况下,由于架构是开放的,因此您不必花钱设计兼容的处理器。与所有开源项目一样,支持该架构的社区正在不断增长,以及参与开发的公司。这些公司之一是 Microchip。

正如我们在 Arm Cortex®-M1 或最近的 Arm Cortex-M3 中看到的那样,还有大量基于 RISC-V 架构的软核可以在 FPGA 上实现。在这篇文章中,我们将使用可用于 Microchip FPGA 的内核Mi-V内核来开发基于 RISC-V 的示例设计。

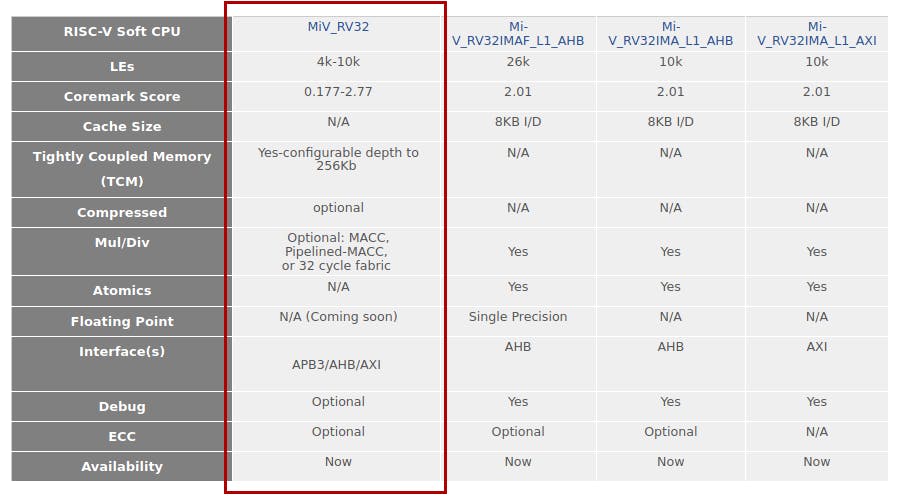

Microchip 提供多个基于 RISC-V 架构的内核。对于这个项目,我们将使用最新开发的内核 MiV_RV32,它是最轻的,因此我们将能够在 Hello FPGA Kit 中进行设计,并且具有可用的 APB3 和 AHB 接口,这对于连接 eNVM 和一些外围设备。

RISC-V 的另一个特点是高可配置性,我们可以根据它们实现的扩展找到不同的基于 RISC-V 的内核。核心中可用的扩展对应于您可以在 RV32 之后找到的字母,例如 RV32IMAF 具有 I(基本整数指令集)、M(整数乘法和除法的标准扩展)、A(原子标准扩展指令)和 F(单精度浮点的标准扩展)。MiV_RV32 内核可用的扩展是 IMC,C 对应于(压缩指令的标准扩展)。

我们要开发的项目将基于 Mi-V_RV32IMC,由于 SmartFusion2 SoC 有一个微控制器子系统 (MSS),我们将 Mi-V 处理器连接到 MSS 以使用非易失性存储器 (eNVM ),以及可用的 SRAM。此外,我们将添加一个能够读取按钮状态的 GPIO 外设和一个脉冲宽度调制 (PWM) 外设来管理板上的三个 LED。在这种情况下,将禁用 Arm Cortex-M3 处理器以节省能源。

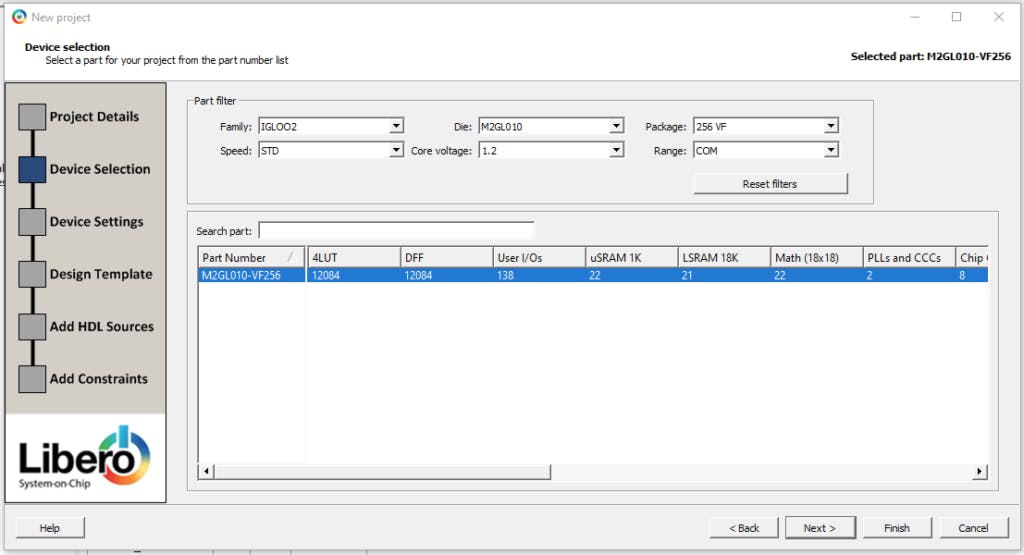

首先,我们必须在 Libero 设计套件上创建一个新项目,选择一个名称,这次,由于我们不会使用 Arm Cortex-M3,我们将选择 IGLOO®2 FPGA 作为一部分,即兼容的 FPGA使用 SmartFusion2 SoC。

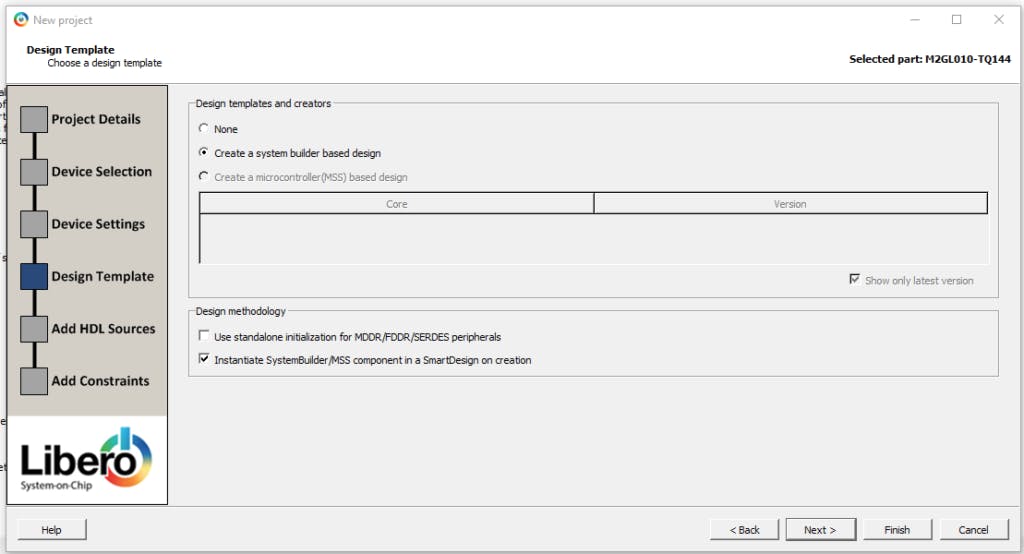

接下来在电压选择器上,我们将为 PLL 和 I/O 设置选择 3.3。现在在下一个窗口中,由于我们将使用 MSS,我们将选择选项Create a system builder-based design 。

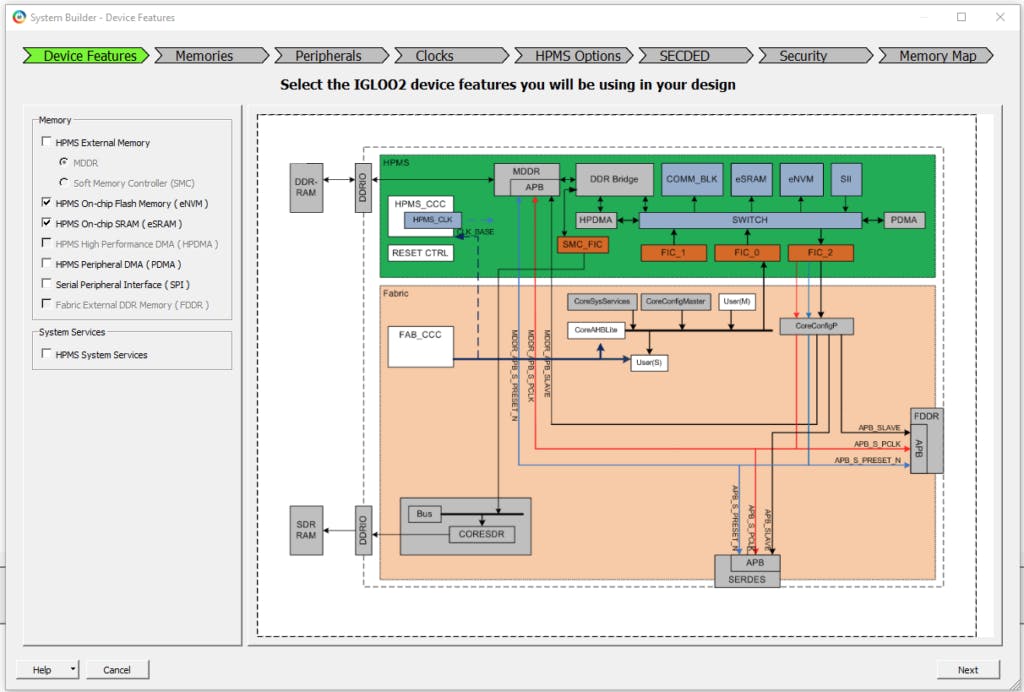

创建项目后,Libero® 设计套件会询问我们系统构建器的名称,在我的例子中,我选择 top 作为名称。接下来,将打开 MSS 配置向导并显示内存选择窗口。在 MSS 中,我们将作为存储程序的 eNVM 和执行程序的 SRAM,因此我们将选择这两个选项。

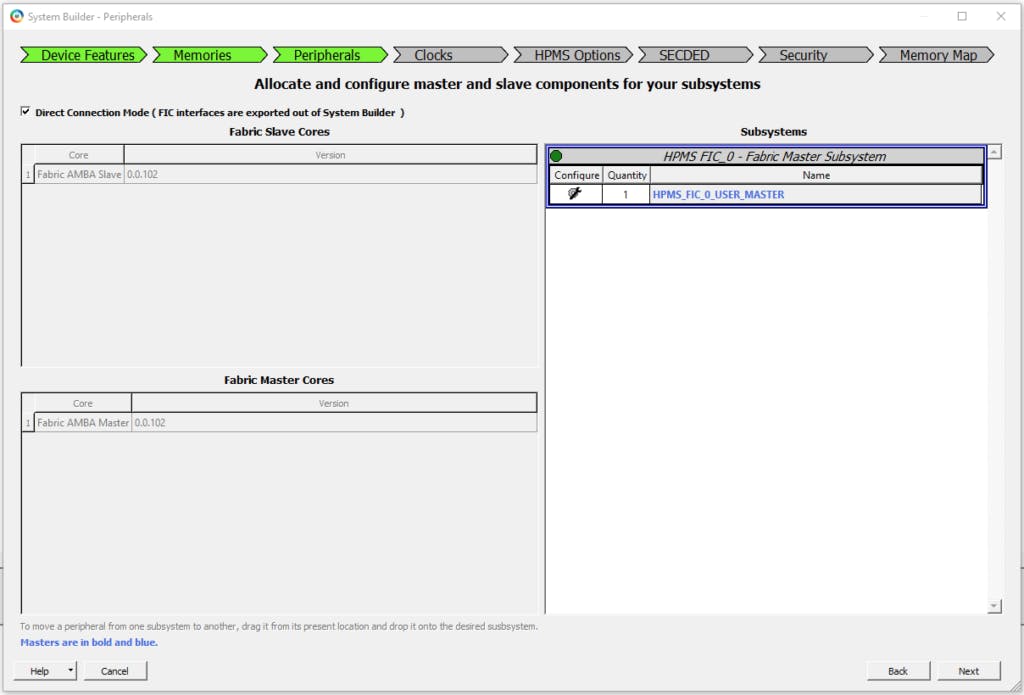

现在我们必须创建一个内存客户端,目前我们将选择选项内容用 0 填充,因为稍后我们将使用 SoftConsole 上生成的 hex 文件初始化内存。通过单击下一步,我们将选择外围设备。在这种情况下,外围设备是 MSS 和结构之间的接口。我们必须选中窗口顶部的框,单击下一步。

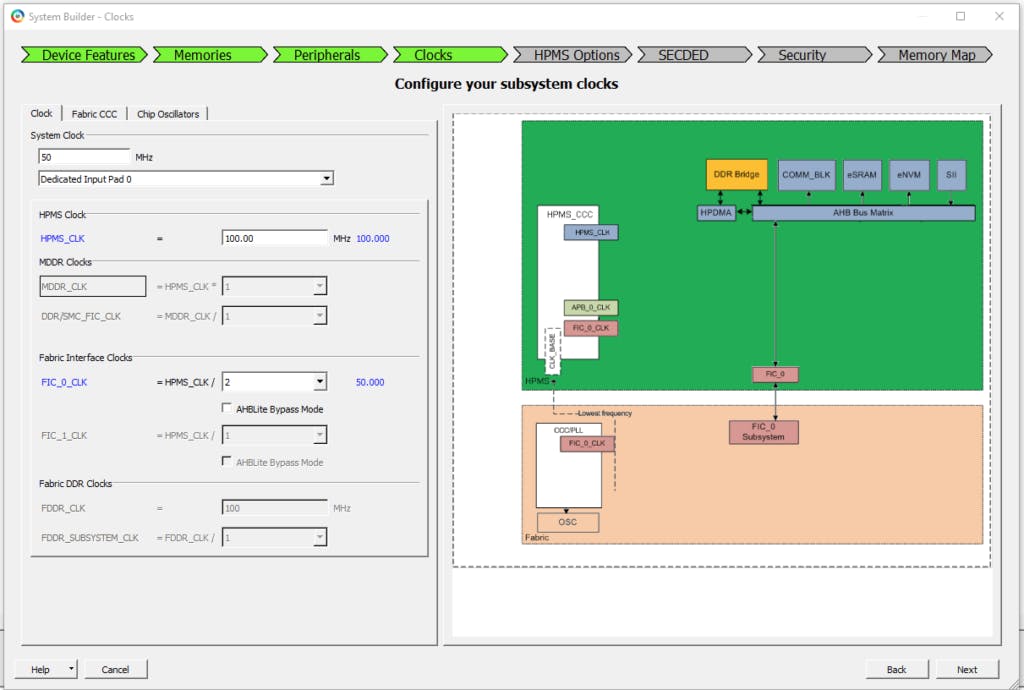

在下一个窗口中,我们可以选择我们想要使用的时钟电路。Hello FPGA 套件有一个板载 50 MHz 振荡器,我们将使用它来为 MSS 时钟电路供电。MSS 的输出时钟将连接到所有结构模块。选择合适的时钟速度很重要,因为 Mi-V 内核将在结构上实现,我们可能会遇到时序问题。现在,我们将为 50 Mhz 的结构选择一个时钟。

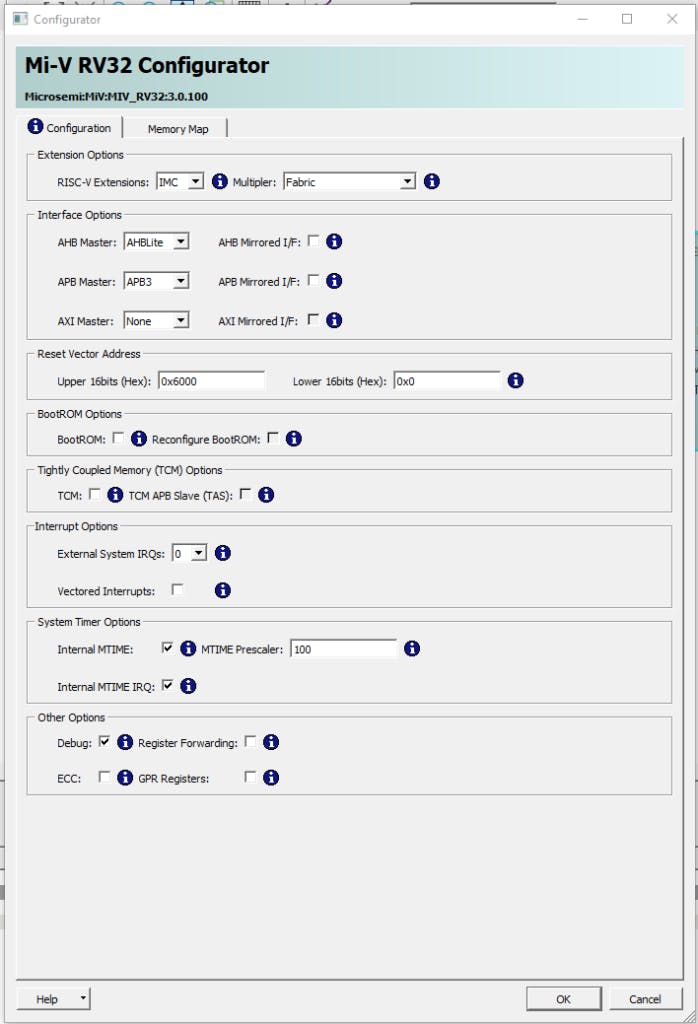

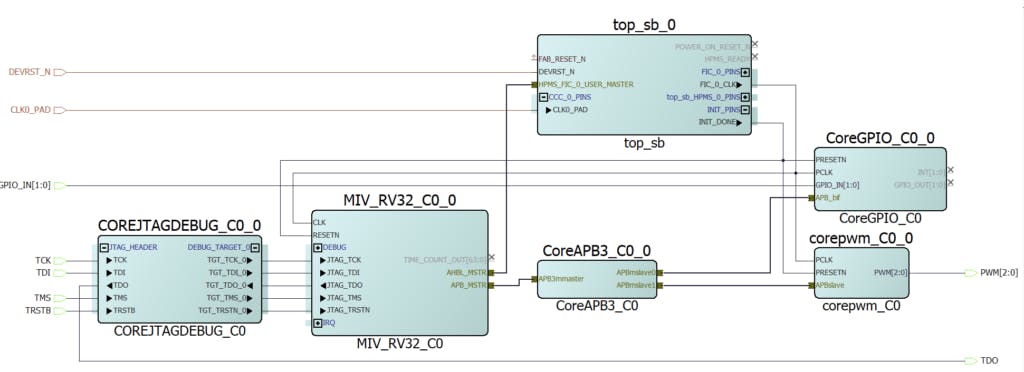

其余窗口将保持默认。向导完成后,我们将拥有一个包含 MSS 的 SmartDesign。现在我们必须在设计中添加我们需要的其余块。我们将从 Mi-V_RV32 内核开始。我们可以在目录选项卡的处理器文件夹中找到它。核心的配置器将被打开。在第一个选项卡上,我们必须选择要添加到核心的扩展,在本例中为 IMC,以及乘法器的位置。此外,我们可以选择我们需要的接口选项,在这种情况下,APB_master 用于外围设备,AHB Master 用于内存。复位向量地址将被配置为 MSS 上 eNVM 内存上的第一个地址,即 0x6000 0000。

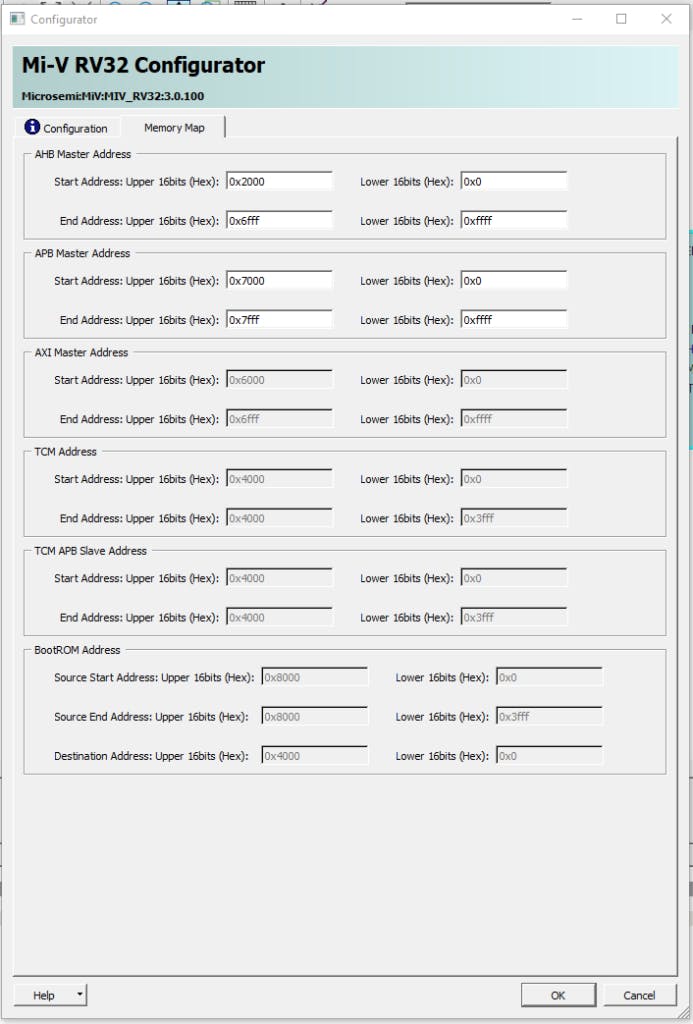

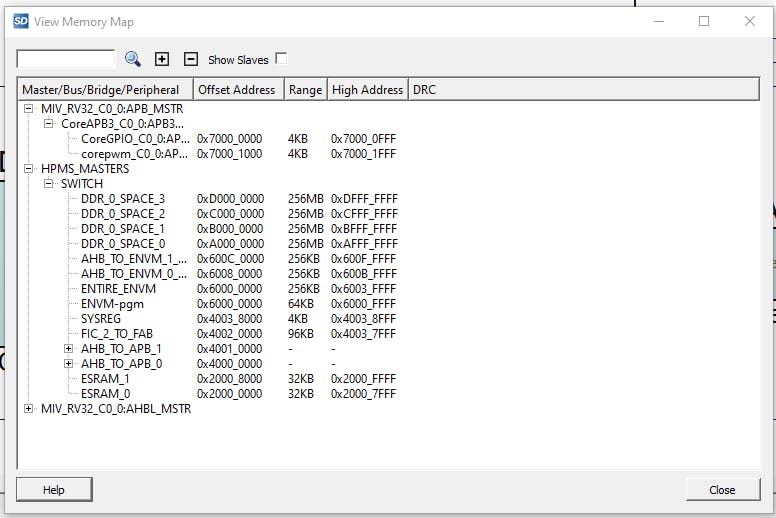

在 Memory Map 选项卡上,我们必须配置接口的地址范围。由于 MSS 有预定义地址,我们必须将 AHB Master 地址配置在 0x2000 0000 到 0x6FFF FFFF 的范围内,连接到 APB 总线的外设将位于 0x7000 0000 到 0x7FFF FFFF 的范围内。

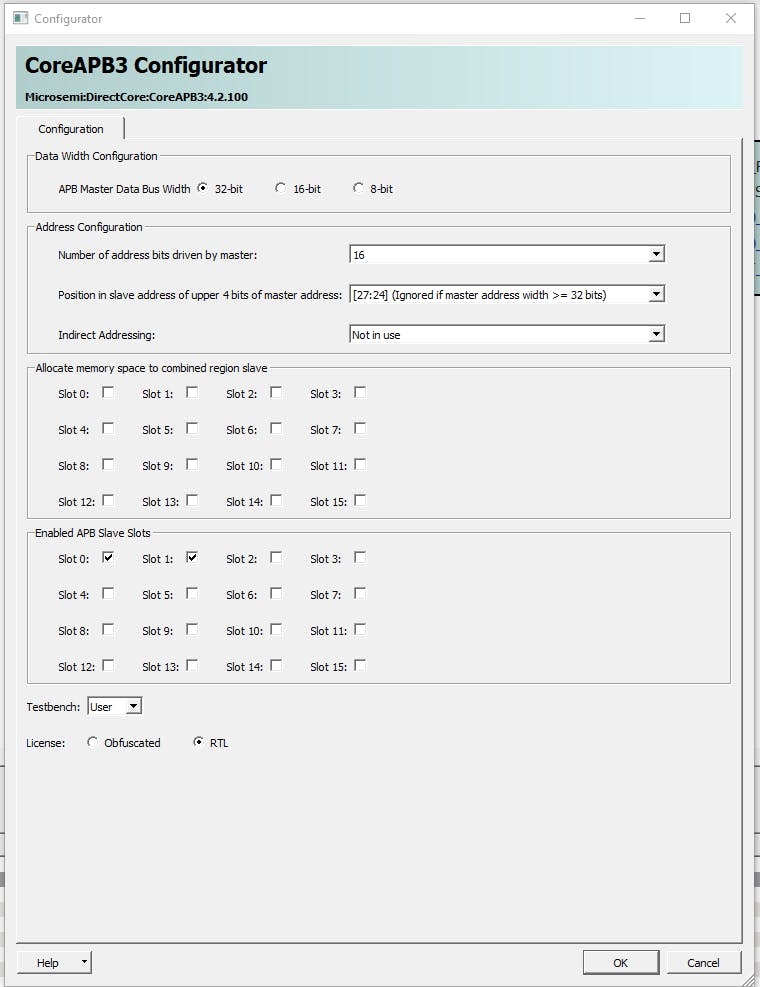

现在 Mi-V 内核已配置并添加到设计中。现在我们必须添加一个带有两个启用 APB 插槽的 CoreAPB3 来连接一个带有三个通道的 corePWM,以及一个带有 2 个 GPIO 的 coreGPIO 来连接按钮。coreAPB3 的地址宽度设置为 16 位。

最后,为了能够调试 Mi-V 内核,我们必须添加一个 coreJTAG。将所有内核添加到 SmartDesign 后,我们必须像下图一样连接所有内核。为避免在设计规则检查中出现警告,请记住将所有未连接的输出标记为未使用。

完成所有设计后,我们必须检查设计规则并生成组件。然后我们可以综合设计。

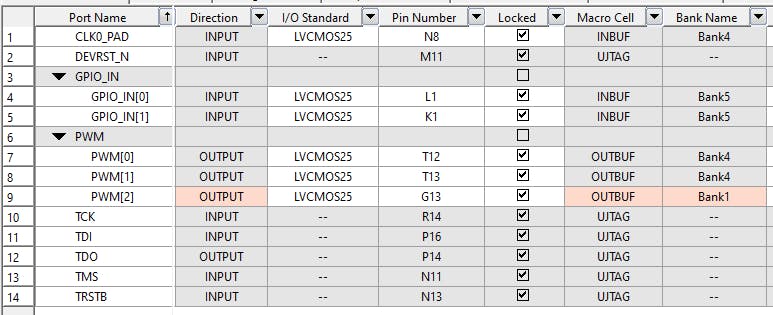

综合设计后,我们可以设置 IO 约束以选择输入和输出引脚。我们必须打开约束管理器,并使用 IO 编辑器通过单击编辑来编辑约束。在 IO 编辑器窗口中,我们必须根据下图选择引脚。

当所有管脚都配置好后,保存并退出 IO Editor,现在我们可以在设计流程上实现设计执行Place and Route 。

现在,由于设计是在结构上实现的,我们必须检查设计的时序。根据手册(第 7 页),SmartFusion2 SoC 上的 Mi-V 可以达到 49 到 65 MHz 之间,具体取决于启用的功能。在这种情况下,设计以 50 MHz 运行,因此显然我们不会有任何问题。要检查时序,首先我们必须定义设计的时序约束。为此,我们将让 Libero 设计套件选择时钟,并设置相应的错误路径。在 Constraint Manager 中,我们将导航到 Timing 选项卡,然后单击Derive constraints 。这将为我们的设计生成一个包含时序约束的文件。我们可以检查这个文件并验证输入时钟和来自 CCC 的输出时钟是否正确定义。

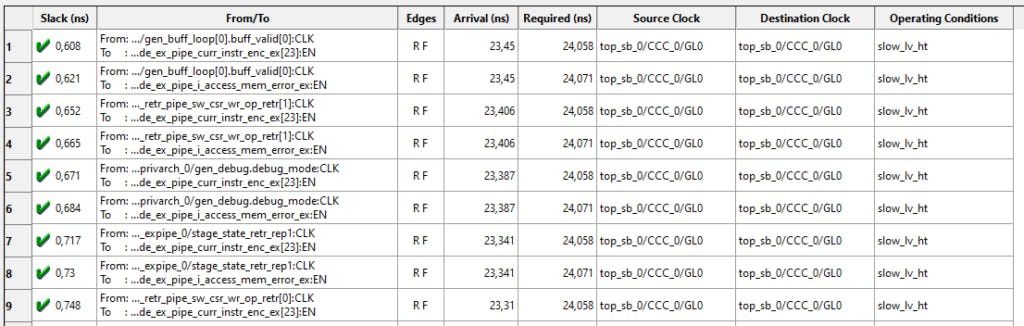

现在,在设计流程中,我们可以执行验证时序命令并等待验证完成。然后我们可以检查一个列表,其中包含根据最差延迟排序的信号。

我们可以看到最慢的信号有 0.608ns 的松弛。

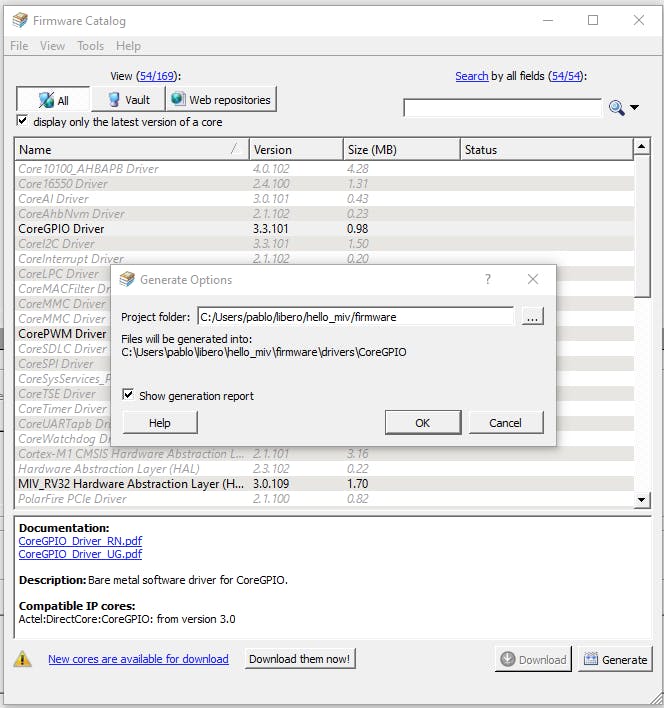

现在,我们必须生成要在软件话务台上使用的所有软件工件。为此,我们必须打开 Libero 设计套件默认安装的固件目录。我们可以看到我们计算机上所有驱动程序的列表。在这种情况下,我们需要为 CoreGPIO、CorePWM 和 MiV_RV32 硬件抽象层 (HAL) 生成驱动程序。

此外,我们将为 corePWM 生成示例项目 PWM Slow Blink 以将其用作模板。

在软件话务台上,我们将导入示例项目,我们必须进行一些更改。首先,我们必须根据地址映射更改 hw_platform 上的地址。

我们可以看到coreGPIO在地址0x7000 0000,corePWM在地址0x7000 1000。在hw_platform.h文件中我们要修改corePWM和coreGPIO对应的地址,还要修改SYS_CLK_FREQ的定义到相应的频率。

#ifndef HW_PLATFORM_H

#define HW_PLATFORM_H

/***************************************************************************//**

* Soft-processor clock definition

* This is the only clock brought over from the Mi-V Soft processor Libero design.

*/

#define SYS_CLK_FREQ 25000000UL

/***************************************************************************//**

* Non-memory Peripheral base addresses

* Format of define is:

* <corename>_<instance>_BASE_ADDR

*/

#define COREGPIO_BASE_ADDR 0x70000000UL

#define COREPWM_BASE_ADDR 0x70001000UL

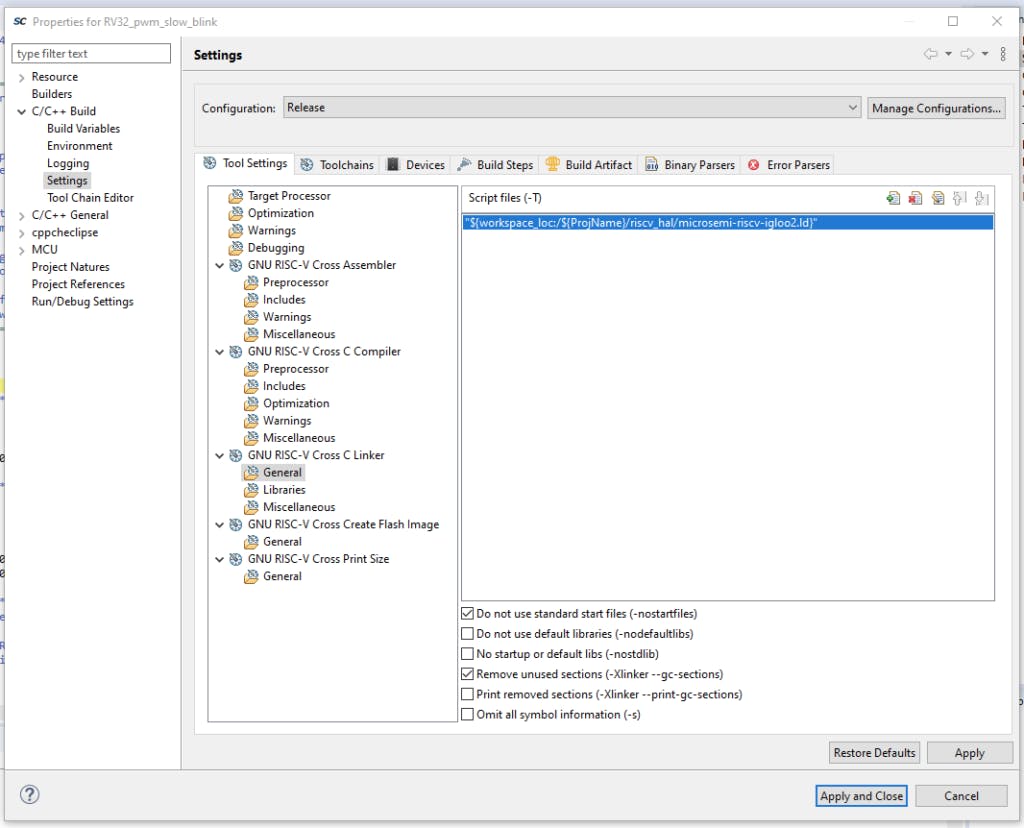

现在,我们必须更改链接器文件以使 RAM 和 ROM 地址与设计匹配。我们将使用的链接器是 microsemi-riscv-igloo2.ld,因为它是从 eNVM 执行代码的模板。在代码中,我们必须更改 eNVM 和 ram 地址。

MEMORY

{

envm (rx) : ORIGIN = 0x60000000, LENGTH = 240k

ram (rwx) : ORIGIN = 0x20000000, LENGTH = 64k

}

RAM_START_ADDRESS = 0x20000000; /* Must be the same value MEMORY region ram ORIGIN above. */

RAM_SIZE = 64k; /* Must be the same value MEMORY region ram LENGTH above. */

STACK_SIZE = 2k; /* needs to be calculated for your application */

HEAP_SIZE = 2k; /* needs to be calculated for your application */

最后,在项目配置上,我们还要再做两处改动。首先,在 C/C++ Build > Settings 上,在链接器配置上,我们必须为Release构建配置选择链接器文件 microsemi-riscv-igloo2.ld。

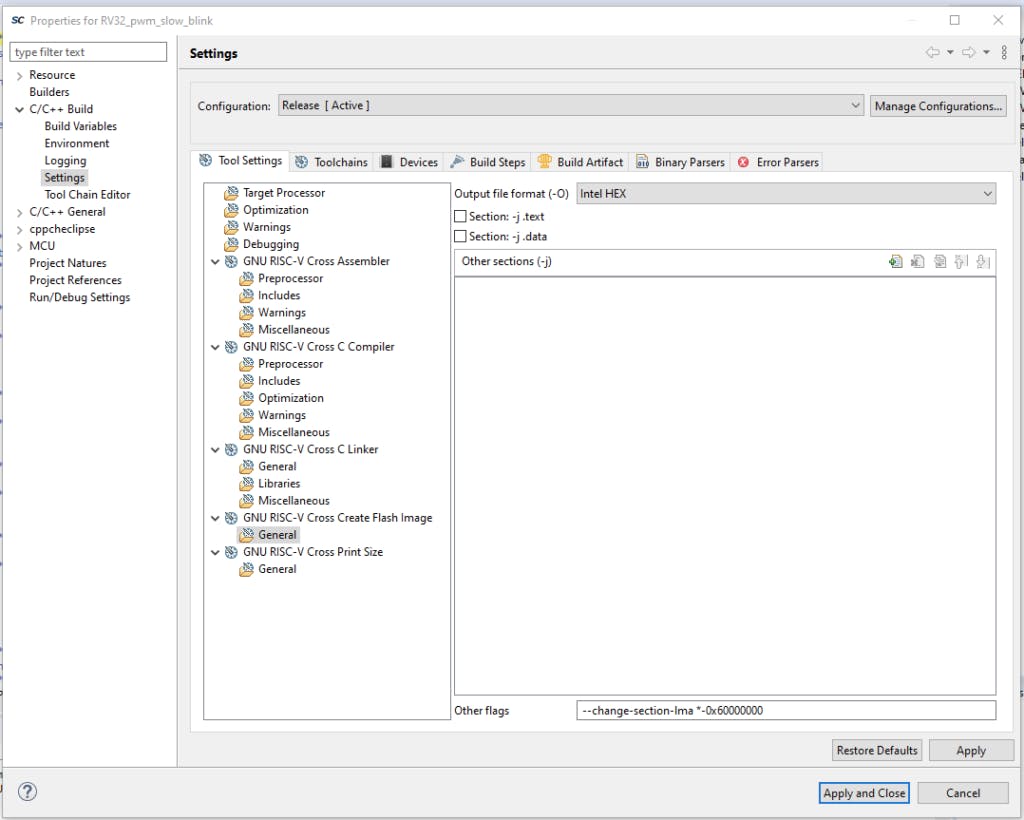

最后,在 Flash 图像创建窗口中,我们必须添加标志 –change-section-lma *-0x60000000

现在我们可以构建项目以生成 hex 文件。

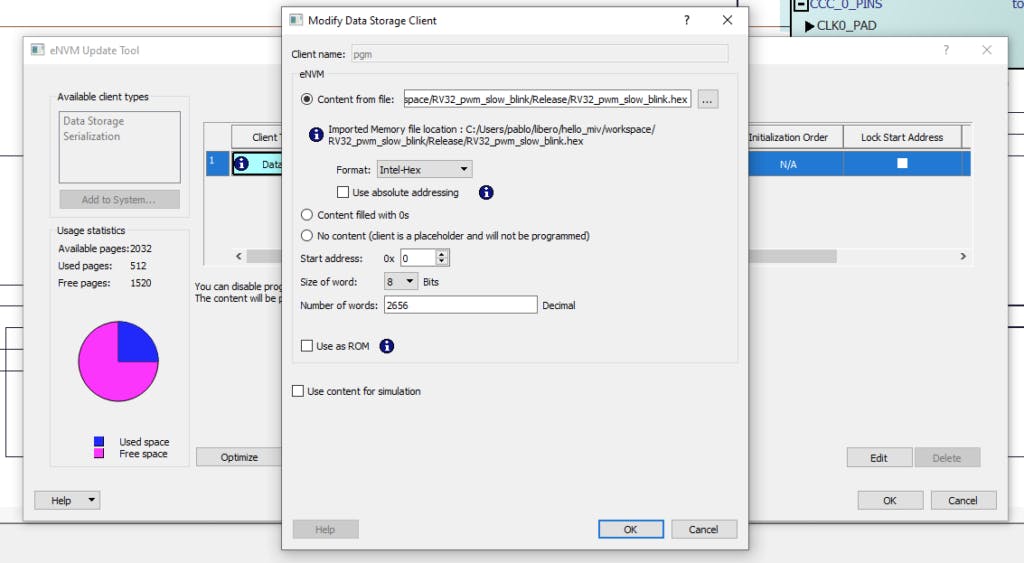

生成 hex 文件后,我们必须回到 Libero 设计套件,并使用生成的 hex 文件初始化 eNVM 内存。

最后生成比特流,并将其导出为 DAT 格式。

现在,我们必须打开 Hello GUI 应用程序将设计发送到 Hello FPGA Kit,我们将看到 LD1 是如何缓慢闪烁的。

虽然 RISC-V 是开源的并且可以免费使用,但也有一些公司已经开发了内核并且可以集成到其他设备中。Microchip 的PolarFire® SoC设备就是这种情况,它们是基于 SiFive 处理器(SiFive 公司的 RISC-V 处理器)的SOC。

我们生活在硅公司的不断变化的时代,尽管 Arm 在该领域拥有大量(大量、大量……)设备,但 RISC-V 使新设备的开发成本更低,而且该标准提供的可配置性可以提供帮助在不需要完整功能的芯片上节省硅。期待使用 RISC-V 的新 SoC。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

-

cooldog123pp

2025-07-09

0 回复 举报很好的资料 收起回复

cooldog123pp

2025-07-09

0 回复 举报很好的资料 收起回复

- 相关下载

- 相关文章