资料下载

如何使用FPGA实现八位RISC CPU的设计

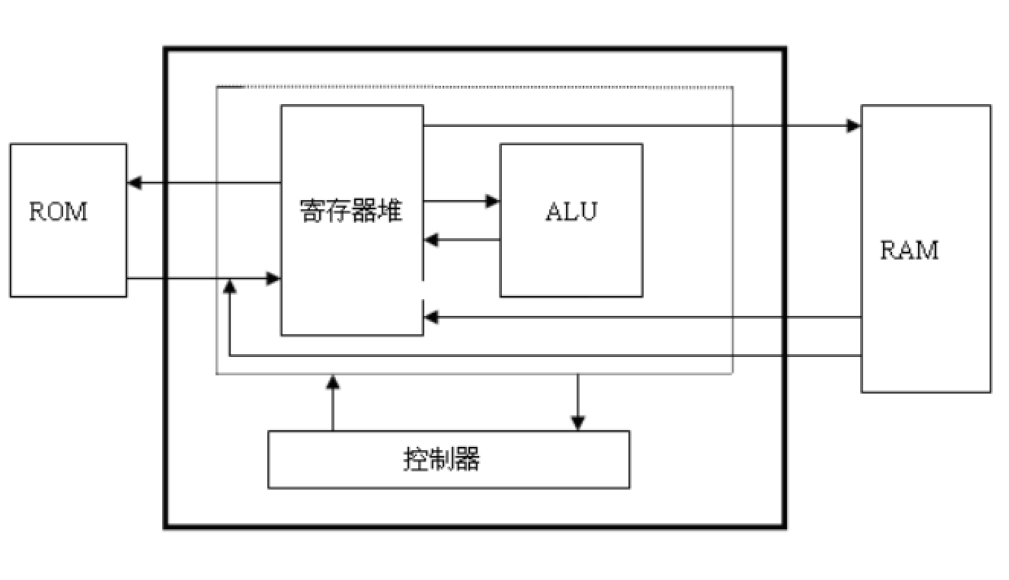

从CPU的总体结构到局部功能的实现采用了自顶向下的设计方法和模块化的设计思想, 利用Xilinx 公司的Spartan II 系列FPGA, 设计实现了八位CPU软核。在FPGA 内部不仅实现了CPU必需的算术逻辑器、寄存器堆、指令缓冲、跳转计数、指令集,而且针对FPGA内部的结构特点对设计进行了地址和数据的优化。

随着数字通信和工业控制领域的高速发展, 要求专用集成电路( ASIC) 的功能越来越强, 功耗越来越低, 生产周期越来越短, 这些都对芯片设计提出了巨大的挑战, 传统的芯片设计方法已经不能适应复杂的应用需求了。SoC( System on a Chip) 以其高集成度,低功耗等优点越来越受欢迎。开发人员不必从单个逻辑门开始去设计ASIC,而是应用己有IC 芯片的功能模块,称为核( core ),或知识产权( IP )宏单元进行快速设计,效率大为提高。CPU 的IP 核是SoC 技术的核心, 开发出具有自主知识产权的CPU IP 核对我国在电子技术方面跟上世界先进的步伐, 提高信息产业在世界上的核心竟争力有重大意义。

精简指令集计算机RISC( Reduced Instruction Set Computer)是针对复杂指令集计算机CISC( Complex Instruction Set Computer) 提出的, 具备如下特征1) 一个有限的简单的指令集; 2)强调寄存器的使用或CPU配备大量的能用的寄存器;3)强调对指令流水线的使用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章