资料下载

×

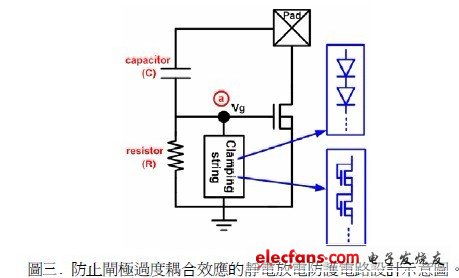

避免闸极过度耦合效应的静电放电防护电路设计

消耗积分:0 |

格式:pdf |

大小:551 KB |

2011-11-30

在深次微米半导体製程中,由于元件尺寸微缩,元件的静电放电(ElectrostaticDischarge,ESD) 耐受度相对变差,因此静电放电防护设计在IC 设计时即必需被加入考量 [1]。通常商用IC 的静电放电耐受度必需通过人体放电模式(HumanBody Model, HBM) 2 kV 与机器放电模式(Machine Model, MM) 200 V 的测试[2]。为了能够承受如此高电压的静电放电测试,IC 上的静电放电防护元件常具有大元件尺寸的设计。为了尽可能节省晶粒面积,在佈局(layout)上,这种大尺寸的元件通常以指状(multi-finger)的方式来实现

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章