资料下载

新型高电源抑制比CMOS电流基准

一种新型的高电源抑制比基准电流源电路的设计

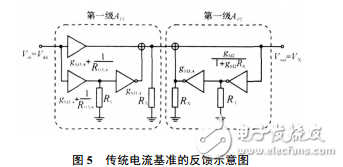

为提高 CMOS 集成电路中电流基准的精度和稳定性, 提出了一种结构简单, 电源抑制比(PSRR)很高的电流基准结构———三支路电流基准。应用基尔霍夫定律(Kirchho ff‘ s curre nt and v oltage law , Kcl Kvl)和偏微分方程, 对比分析了传统的电流基准、共源共栅电流基准以及三支路电流基准的小信号模型, 求解出了这 3 种电路的电源抑制比公式。对比发现传统电流基准和共源共栅电流基准的节点电压正反馈限制了电流基准的性能, 三支路结构由于节点电压成强负反馈, 拥有更高的 PSRR.三支路电流基准采用了一阶温度补偿方案, 保证了温度稳定性。经 CSMC 0.5 μm 工艺仿真结果显示, 三支路基准在输入电压 1.5 ~ 5 .0 V 的低频 PS RR 达-77 .9 dB , 明显优于另外两种结构;在-20~ 120 ℃温度区间内输出电流稳定性达到了 255 ×10 -6 / ℃, 满足了大多数应用的要求。

在低功耗、高精度模拟集成电路设计中, 纳安级电流基准经常是不可缺少的。但在纳安级小电流下 , 要得到更小的温度漂移 、更大的输出电阻 Rout 和更大的电 源抑制 比(power supply rejection ratio , PS RR)[ 1] 就比较困难 。现有的设计中常用的电流基准包括传统结构 [ 1] 和共源共栅(Cascode) [ 2-3] 结构。

虽然通过温度补偿 [ 4-5] 可以得到比较理想的电流温度特性 ,但在 Rout和 PS RR 方面 ,尽管共源共栅结构比传统电流基准有很大提高[ 2-3] , 但性能仍不理想 。 主要原因是,共源共栅电流基准的节点电压有正反馈关系 [ 3] ,限制了 PS RR 进一步提高。因此有必要对电流基准 PS RR 性能问题进行深入分析 。 本文采用基尔霍夫定律[ 6] 分析了电流基准的 PSRR ,并设计了一种大幅提高 PS RR 的电流基准 : 三支路电流基准 , 并在 Cadence Spectre 仿真器和 CSM C 0 .5 μm 混合信号模型下对这种设计方案的效果进行了验证 。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章