资料下载

mpc5644a单片机数据表

This addendum describes corrections to the MPC5644A Microcontroller Datasheet, order number MPC5644A. For convenience, the addenda items are grouped by revision. Please check our website at http://www.freescale.com/powerarchitecture for the latest updates. The current version available of the MPC5644A Microcontroller Datasheet is Revision 7.

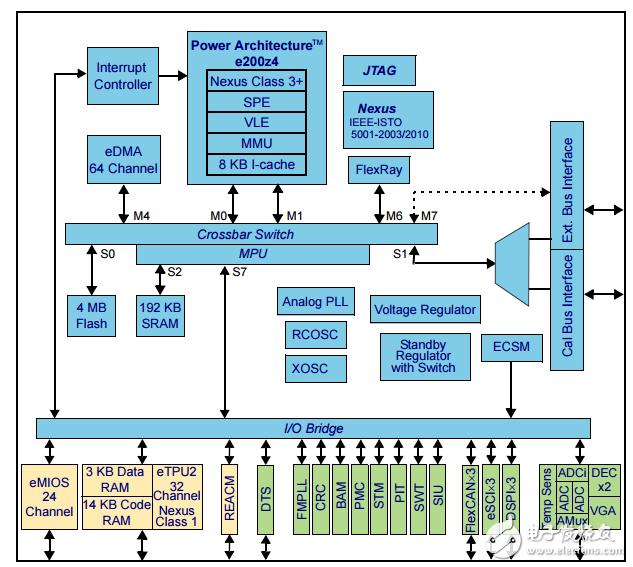

1.1 Document Overview This document provides electrical specifications, pin assignments, and package diagrams for the MPC5644A series of microcontroller units (MCUs)。 For functional characteristics, refer to the MPC5644A Microcontroller Reference Manual. 1.2 Description The microcontroller’s e200z4 host processor core is built on Power Architecture® technology and designed specifically for embedded applications. In addition to the Power Architecture technology, this core supports instructions for digital signal processing (DSP)。 The MPC5644A has two levels of memory hierarchy consisting of 8 KB of instruction cache, backed by 192 KB on-chip SRAM and 4 MB of internal flash memory. The MPC5644A includes an external bus interface, and also a calibration bus that is only accessible when using the Freescale VertiCal Calibration System. This document describes the features of the MPC5644A and highlights important electrical and physical characteristics of the device.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章