资料下载

×

通用嵌入式存储器模型设计方案探究

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-10-16

1引言

建立芯片模型是在早期进行芯片架构决策的有效方法,通过建模不仅可以对芯片的性能做出分析,还可以在硬件没有完成之前开发软件,不仅提高了产品成功率,而且缩短了研发周期。设计人员早期采用C/C++语言进行硬件建模。但是随着软硬件复杂度的提高,C/C++语言难以再满足要求。OSCI适时推出了SystemC语言来适应新的需求。如今SystemC已经被广泛应用于SoC软硬件建模中。

目前大部分SystemC建模方面的文献是作者对自己所设计芯片整体模型的描述,这种针对特定芯片设计的文献虽然都有参考价值,但是其模型本身借鉴性有限。另一方面,构成SoC硬件的基本组件因为可重用的缘故,其模型设计具有更好的可借鉴性。这方面的研究成果相对较少,而且集中在总线建模方面,也可以看到多核设计方面的建模方法。

除了上述总线、CPU架构外,片内或片外存储器同样是系统关键模块,对系统性能有着至关重要的影响。文献[6]对SystemClick框架做了扩展,从而通过存储器模型能够分析共享存储器对性能的影响。文献[7]针对多通道DRAM做了建模,并且分析了不同的配置和使用情况对性能的影响。这两篇文献都对所设计的模型做了详尽的分析,具有很好的参考价值,但是两者的通用性欠佳。本文提出了一个可配置的通用存储器SystemC模型。

2 SystemC

SystemC可被视作C++硬件建模和仿真的扩展库,特别适合集成电路的建模,但它事实上可以用来描述更多的系统。SystemC通过确定仿真核心(simulation kernel)算法定义了处理并行事件和仿真时间的机制。SystemC还定义了模块、端口、接口、通道等概念来组成一个复杂SoC的连接关系和层次结构。因此,它解决了标准C++语言用于复杂硬件建模时的难题。

3存储器的建模

3.1存储器模型概述

为了能帮助设计人员分析系统性能并选择最合适的存储器构造,存储器模型需要反映出对性能造成影响的关键参数,即带宽、延时和仲裁机制。而这些参数又是由存储器的结构以及其它参数决定的。另一方面,本文希望提出一个通用的存储器模型,因此会有更多的参数用于配置存储器以模拟某种特定类型的存储器特征,比如多端口SRAM.

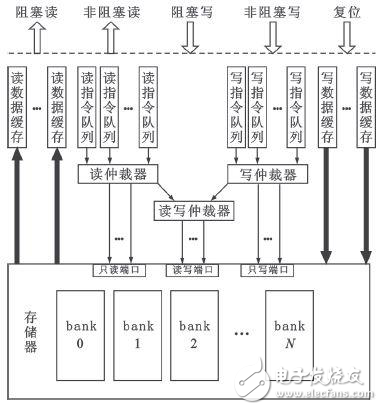

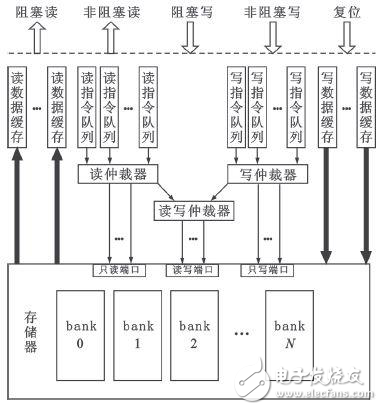

图1给出了所设计的存储器模型的结构。它包括三个部分:一是模型接口;二是端口及bank可配置的存储器;三是由读写通路及仲裁机制构成的存储器控制器。接口部分采用了事务级建模,而内部模块采用了时钟精准的建模,这样在保证时间精度的同时,方便了接口连接以及提高了仿真速度。

图1可配置存储器模型结构

3.2存储器接口

基于SystemC的存储器模型接口,由SystemC定义的接口基类派生而来。整个存储器模型是一个SystemC模块,由于实现了所定义的存储器模型接口,它成为SystemC概念中的hierarchal channel.因此,该存储器模型将如同其它SystemC定义的通道,比如FIFO,一样作为基本组件来连接其它的模块从而构造出SoC硬件系统。所设计存储器具有如下所述事务级SystemC接口。

阻塞读接口:该接口用来读取给定地址的给定大小的数据,当数据没有读出时,调用这个接口的模块线程将被堵塞,直到数据读出为止。除了地址和数据,该接口还包含调用者的标志信息。

非阻塞读接口:与阻塞读接口不同的是,如果在调用时读指令不能被接受,则返回失败。否则,不等待数据返回便成功退出。这样调用接口的模块线程可以在等待时间做其它事情。调用者通过监听存储器模型广播的当前读出数据多对应调用者标记来在之后读出数据。

阻塞写接口:该接口用来向存储器给定地址写入给定大小的数据。当指令或写数据不能被存储器模型接收时,调用的线程被堵塞直到接受为止。除了地址和数据,该接口还包含调用者的标志信息。

非阻塞写接口:与阻塞写接口不同的是,当指令或数据不能被接受时,返回失败而不等待。否则返回成功。

复位接口:用于复位存储器模型。

为了不强制要求外部提供存储器模型需要的时钟,存储器模型接口中不包含时钟输入。模型内部有一个专门的时钟产生线程。

建立芯片模型是在早期进行芯片架构决策的有效方法,通过建模不仅可以对芯片的性能做出分析,还可以在硬件没有完成之前开发软件,不仅提高了产品成功率,而且缩短了研发周期。设计人员早期采用C/C++语言进行硬件建模。但是随着软硬件复杂度的提高,C/C++语言难以再满足要求。OSCI适时推出了SystemC语言来适应新的需求。如今SystemC已经被广泛应用于SoC软硬件建模中。

目前大部分SystemC建模方面的文献是作者对自己所设计芯片整体模型的描述,这种针对特定芯片设计的文献虽然都有参考价值,但是其模型本身借鉴性有限。另一方面,构成SoC硬件的基本组件因为可重用的缘故,其模型设计具有更好的可借鉴性。这方面的研究成果相对较少,而且集中在总线建模方面,也可以看到多核设计方面的建模方法。

除了上述总线、CPU架构外,片内或片外存储器同样是系统关键模块,对系统性能有着至关重要的影响。文献[6]对SystemClick框架做了扩展,从而通过存储器模型能够分析共享存储器对性能的影响。文献[7]针对多通道DRAM做了建模,并且分析了不同的配置和使用情况对性能的影响。这两篇文献都对所设计的模型做了详尽的分析,具有很好的参考价值,但是两者的通用性欠佳。本文提出了一个可配置的通用存储器SystemC模型。

2 SystemC

SystemC可被视作C++硬件建模和仿真的扩展库,特别适合集成电路的建模,但它事实上可以用来描述更多的系统。SystemC通过确定仿真核心(simulation kernel)算法定义了处理并行事件和仿真时间的机制。SystemC还定义了模块、端口、接口、通道等概念来组成一个复杂SoC的连接关系和层次结构。因此,它解决了标准C++语言用于复杂硬件建模时的难题。

3存储器的建模

3.1存储器模型概述

为了能帮助设计人员分析系统性能并选择最合适的存储器构造,存储器模型需要反映出对性能造成影响的关键参数,即带宽、延时和仲裁机制。而这些参数又是由存储器的结构以及其它参数决定的。另一方面,本文希望提出一个通用的存储器模型,因此会有更多的参数用于配置存储器以模拟某种特定类型的存储器特征,比如多端口SRAM.

图1给出了所设计的存储器模型的结构。它包括三个部分:一是模型接口;二是端口及bank可配置的存储器;三是由读写通路及仲裁机制构成的存储器控制器。接口部分采用了事务级建模,而内部模块采用了时钟精准的建模,这样在保证时间精度的同时,方便了接口连接以及提高了仿真速度。

图1可配置存储器模型结构

3.2存储器接口

基于SystemC的存储器模型接口,由SystemC定义的接口基类派生而来。整个存储器模型是一个SystemC模块,由于实现了所定义的存储器模型接口,它成为SystemC概念中的hierarchal channel.因此,该存储器模型将如同其它SystemC定义的通道,比如FIFO,一样作为基本组件来连接其它的模块从而构造出SoC硬件系统。所设计存储器具有如下所述事务级SystemC接口。

阻塞读接口:该接口用来读取给定地址的给定大小的数据,当数据没有读出时,调用这个接口的模块线程将被堵塞,直到数据读出为止。除了地址和数据,该接口还包含调用者的标志信息。

非阻塞读接口:与阻塞读接口不同的是,如果在调用时读指令不能被接受,则返回失败。否则,不等待数据返回便成功退出。这样调用接口的模块线程可以在等待时间做其它事情。调用者通过监听存储器模型广播的当前读出数据多对应调用者标记来在之后读出数据。

阻塞写接口:该接口用来向存储器给定地址写入给定大小的数据。当指令或写数据不能被存储器模型接收时,调用的线程被堵塞直到接受为止。除了地址和数据,该接口还包含调用者的标志信息。

非阻塞写接口:与阻塞写接口不同的是,当指令或数据不能被接受时,返回失败而不等待。否则返回成功。

复位接口:用于复位存储器模型。

为了不强制要求外部提供存储器模型需要的时钟,存储器模型接口中不包含时钟输入。模型内部有一个专门的时钟产生线程。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章