资料下载

×

数字钟实验电路的设计方案分析

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-10-19

在电子技术实验教学中,构建学生的电路设计理念,提高学生的电路设计能力,是教学的根本目的和核心内容。数字钟电路的设计和仿真,涉及模拟电子技术、数字电子技术等多方面知识,能够体现实验者的理论功底和设计水平,是电子设计和仿真教学的典型案例。文中采用了555 定时器电路、计数电路、译码电路、显示电路和时钟校正电路,来实现该电路。

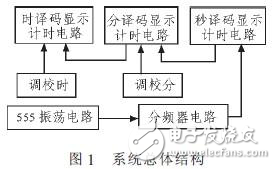

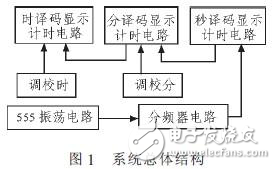

1 系统设计方案

数字钟由振荡器、分频器、计时电路、译码显示电路等组成[1-3]。振荡器是数字钟的核心,提供一定频率的方波信号;分频器的作用是进行频率变换,产生频率为1 Hz 的秒信号,作为是整个系统的时基信号; 计时电路是将时基信号进行计数;译码显示电路的作用是显示时、分、秒时间;校正电路用来对时、分进行校对调整。其总体结构图,如图1 所示。

2 子系统的实现

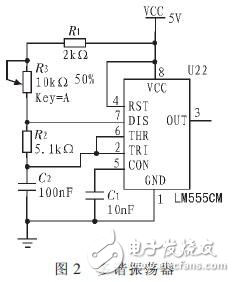

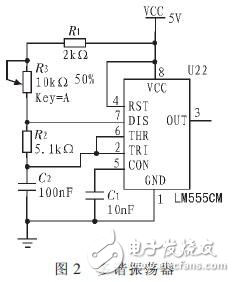

2.1 振荡器

本系统的振荡器采用由555 定时器与RC 组成的多谐振荡器来实现, 如图2 所示即为产生1 kHz 时钟信号的电路图。此多谐振荡器虽然产生的脉冲误差较大,但设计方案快捷、易于实现、受电源电压和温度变化的影响很小[4]。

2.2 分频器

由于振荡器产生的频率高, 要得到标准的秒信号,就需要对所得到的信号进行分频。在此电路中,分频器的功能主要有两个:1) 产生标准脉冲信号;2) 提供电路工作需要的信号,比如扩展电路需要的信号。通常实现分频器的电路是计数器电路,选择74LS160 十进制计数器来完成上述功能[5]。如图3 所示,555 定时器产生1 kHz 的信号,经过3 次1/10 分频后得到1 Hz 的脉冲信号, 为秒个位提供标准秒脉冲信号。

1 系统设计方案

数字钟由振荡器、分频器、计时电路、译码显示电路等组成[1-3]。振荡器是数字钟的核心,提供一定频率的方波信号;分频器的作用是进行频率变换,产生频率为1 Hz 的秒信号,作为是整个系统的时基信号; 计时电路是将时基信号进行计数;译码显示电路的作用是显示时、分、秒时间;校正电路用来对时、分进行校对调整。其总体结构图,如图1 所示。

2 子系统的实现

2.1 振荡器

本系统的振荡器采用由555 定时器与RC 组成的多谐振荡器来实现, 如图2 所示即为产生1 kHz 时钟信号的电路图。此多谐振荡器虽然产生的脉冲误差较大,但设计方案快捷、易于实现、受电源电压和温度变化的影响很小[4]。

2.2 分频器

由于振荡器产生的频率高, 要得到标准的秒信号,就需要对所得到的信号进行分频。在此电路中,分频器的功能主要有两个:1) 产生标准脉冲信号;2) 提供电路工作需要的信号,比如扩展电路需要的信号。通常实现分频器的电路是计数器电路,选择74LS160 十进制计数器来完成上述功能[5]。如图3 所示,555 定时器产生1 kHz 的信号,经过3 次1/10 分频后得到1 Hz 的脉冲信号, 为秒个位提供标准秒脉冲信号。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(1)

发评论

-

秫秫

2020-10-21

0 回复 举报谢谢分享 收起回复

秫秫

2020-10-21

0 回复 举报谢谢分享 收起回复

- 相关下载

- 相关文章