资料下载

×

DSP实时数据无损压缩方案分析

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-10-24

数据压缩技术能减少传输所用的时间和存储空间,在有限的信道容量内传输更多的有用信息,有助于降低功率和带宽要求,改善通信效率。反之,如果不进行数据压缩,则无论传输或存储都很难实用化[1]。

1 硬件及实现原理

结合本设计的实际情况,由于压缩算法比较复杂,计算量大,在压缩数据时必须采用浮点型运算。另一方面,由于处理精度要求高,所以需要选择浮点型DSP。基于上述考虑,选用TI公司的一款性价比非常高的浮点芯片TMS320C6713。其主频225MHz,每周期执行8条32bit指令,最高定点运算能力为 1800MIPS,浮点运算能力为1350MFLOPS,32位指令集,而且内部自带256KB的RAM,4KB程序缓冲器和4KB的数据缓冲器,可以通过外部存储器接口EMIF(External Memory Inter Faces)扩展SDRAM和Flash[2]。在本设计中,对原始数据按照每2 048B为一组进行压缩。压缩的最小单位是2 048B,且压缩率不固定,对于某组特定数据压缩后可能比原来的数据还要大。压缩前后的数据都需要放到DSP的RAM中进行处理,其256KB的RAM不能满足本设计存储要求,需要通过EMIF扩展存储空间。SDRAM选用Micron公司的MT48LC2M32B2。其数据总线为32位,存储空间为 64Mbit。工作电压为3.3V,内部流水线结构保证了芯片的高速运行。SDRAM可以与EMIF无缝接口。EMIF的CE0连入片选引脚CS,将 SDRAM映射到CE0地址空间(0x80000000-0x80800000)。Flash是系统在断电后用来保存程序和初始化数据的存储器,系统上电时,由引导程序将DSP的应用程序从该存储器引导到系统的高速存储器RAM中。本设计用AMD公司生产的1M×8bit/512K×16bit AM29LV800-70 Flash存储器,其数据宽度为8位、16位可选,采用3.3V供电,访问时间仅70ns。EMIF的CE1连入片选引脚CE,将Flash映射到CE1 地址空间地址范围为0x90000000~0x90100000,寻址空间为1MB[3]。

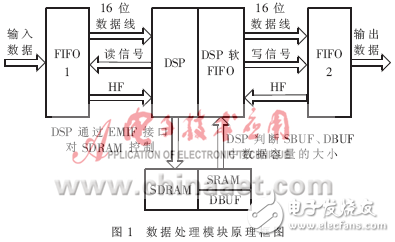

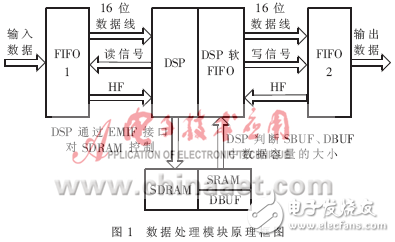

通常在高速数据采集系统中,数据处理速度及数据传输速度与前端A/D转换器的采集速度不一致。为了协调它们之间工作,可以加入数据存储器或者数据缓存器(FIFO)进行数据缓冲,使得前端数据采集和后级数据处理能够协调工作。在本设计中,前端的采样速度为27Kb/s;且数据流是连续的。DSP的主频为 225MHz,经过锁向环分频后其读取数据的速度为38Mb/s左右。DSP若一直等待读数据,会大大降低其数据的处理能力。DSP读入数据后,马上对数据进行压缩,压缩后把相应的数据写到输出FIFO。同理,发送模块的处理速度为18Kb/s。DSP写输出FIFO的速度也在38Mb/s左右。显然,前端与DSP及DSP与发送模块的处理速度不是一个数量级。所以在前端与DSP之间,DSP与发送模块间分别加了两个FIFO。本设计中FIFO1、 FIFO2均选用IDT72V19160,其存储空间为128KB,16位并行数据总线,可达到100MHz的操作时钟。原理框图如图1所示。

前端通过16位数据总线将数据写入到输入FIFO1中。在程序中通过控制其半满(HF)信号,即当数据超过32KB时(32768+1), HF信号低电平有效,就会触发一次中断通知可编程逻辑和DSP,DSP进入中断后把2KB的数据从输入FIFO1中读入到SBUF所指向的SDRAM空间中,在进行高速压缩以后,被压缩的数据放到DBUF中。SBUF的数据要与DBUF的数据进行比较,若DBUF中存储数据的容量小于SBUF中的存储数据的容量,就把DBUF中相应的数据写到DSP的软FIFO中,否则,就把SBUF中相应的数据写到DSP的软FIFO中。最终,DSP把压缩后的数据通过其软FIFO写入到输出FIFO2中,等待发送模块把数据读走。

在上述过程中,如果DSP没有等待到中断信号,则返回继续等待,直到检测到中断信号,才读取FIFO1中的数据。在DSP对SBUF中的数据帧压缩的同时,前端以固定的采样率对模拟信号进行采样,并写入到输入FIFO1中。同时DSP把压缩后的数据按每次小于2KB左右的速度写入到输出FIFO2。当输出FIFO2半满,发送模块控制器会把其HF信号通过GPIO口指向DSP。本设计中用GP10实现相应的操作。DSP的GPIO口可以设为输入引脚,在中断向量表中定义后,其本身可以当作中断使用。这样DSP可以把采集到的实时数据源源不断地写入到FIFO2。整个信号处理模块的不同子模块都处于并行工作状态,较好地实现了数据的实时压缩,提高了压缩效率。

设备上电DSP复位后,由其内部固化的自引导程序(BOOT)将存于Flash存储器的程序和数据搬移至内部 RAM中,然后DSP即可以开始读取压缩算法的应用程序,继续运行。DSP的工作流程图如图2所示。上电以后,首先初始化DSP的CSL函数库,然后初始化PLL、GPIO及关中断寄存器,等待中断信号的来临。

1 硬件及实现原理

结合本设计的实际情况,由于压缩算法比较复杂,计算量大,在压缩数据时必须采用浮点型运算。另一方面,由于处理精度要求高,所以需要选择浮点型DSP。基于上述考虑,选用TI公司的一款性价比非常高的浮点芯片TMS320C6713。其主频225MHz,每周期执行8条32bit指令,最高定点运算能力为 1800MIPS,浮点运算能力为1350MFLOPS,32位指令集,而且内部自带256KB的RAM,4KB程序缓冲器和4KB的数据缓冲器,可以通过外部存储器接口EMIF(External Memory Inter Faces)扩展SDRAM和Flash[2]。在本设计中,对原始数据按照每2 048B为一组进行压缩。压缩的最小单位是2 048B,且压缩率不固定,对于某组特定数据压缩后可能比原来的数据还要大。压缩前后的数据都需要放到DSP的RAM中进行处理,其256KB的RAM不能满足本设计存储要求,需要通过EMIF扩展存储空间。SDRAM选用Micron公司的MT48LC2M32B2。其数据总线为32位,存储空间为 64Mbit。工作电压为3.3V,内部流水线结构保证了芯片的高速运行。SDRAM可以与EMIF无缝接口。EMIF的CE0连入片选引脚CS,将 SDRAM映射到CE0地址空间(0x80000000-0x80800000)。Flash是系统在断电后用来保存程序和初始化数据的存储器,系统上电时,由引导程序将DSP的应用程序从该存储器引导到系统的高速存储器RAM中。本设计用AMD公司生产的1M×8bit/512K×16bit AM29LV800-70 Flash存储器,其数据宽度为8位、16位可选,采用3.3V供电,访问时间仅70ns。EMIF的CE1连入片选引脚CE,将Flash映射到CE1 地址空间地址范围为0x90000000~0x90100000,寻址空间为1MB[3]。

通常在高速数据采集系统中,数据处理速度及数据传输速度与前端A/D转换器的采集速度不一致。为了协调它们之间工作,可以加入数据存储器或者数据缓存器(FIFO)进行数据缓冲,使得前端数据采集和后级数据处理能够协调工作。在本设计中,前端的采样速度为27Kb/s;且数据流是连续的。DSP的主频为 225MHz,经过锁向环分频后其读取数据的速度为38Mb/s左右。DSP若一直等待读数据,会大大降低其数据的处理能力。DSP读入数据后,马上对数据进行压缩,压缩后把相应的数据写到输出FIFO。同理,发送模块的处理速度为18Kb/s。DSP写输出FIFO的速度也在38Mb/s左右。显然,前端与DSP及DSP与发送模块的处理速度不是一个数量级。所以在前端与DSP之间,DSP与发送模块间分别加了两个FIFO。本设计中FIFO1、 FIFO2均选用IDT72V19160,其存储空间为128KB,16位并行数据总线,可达到100MHz的操作时钟。原理框图如图1所示。

前端通过16位数据总线将数据写入到输入FIFO1中。在程序中通过控制其半满(HF)信号,即当数据超过32KB时(32768+1), HF信号低电平有效,就会触发一次中断通知可编程逻辑和DSP,DSP进入中断后把2KB的数据从输入FIFO1中读入到SBUF所指向的SDRAM空间中,在进行高速压缩以后,被压缩的数据放到DBUF中。SBUF的数据要与DBUF的数据进行比较,若DBUF中存储数据的容量小于SBUF中的存储数据的容量,就把DBUF中相应的数据写到DSP的软FIFO中,否则,就把SBUF中相应的数据写到DSP的软FIFO中。最终,DSP把压缩后的数据通过其软FIFO写入到输出FIFO2中,等待发送模块把数据读走。

在上述过程中,如果DSP没有等待到中断信号,则返回继续等待,直到检测到中断信号,才读取FIFO1中的数据。在DSP对SBUF中的数据帧压缩的同时,前端以固定的采样率对模拟信号进行采样,并写入到输入FIFO1中。同时DSP把压缩后的数据按每次小于2KB左右的速度写入到输出FIFO2。当输出FIFO2半满,发送模块控制器会把其HF信号通过GPIO口指向DSP。本设计中用GP10实现相应的操作。DSP的GPIO口可以设为输入引脚,在中断向量表中定义后,其本身可以当作中断使用。这样DSP可以把采集到的实时数据源源不断地写入到FIFO2。整个信号处理模块的不同子模块都处于并行工作状态,较好地实现了数据的实时压缩,提高了压缩效率。

设备上电DSP复位后,由其内部固化的自引导程序(BOOT)将存于Flash存储器的程序和数据搬移至内部 RAM中,然后DSP即可以开始读取压缩算法的应用程序,继续运行。DSP的工作流程图如图2所示。上电以后,首先初始化DSP的CSL函数库,然后初始化PLL、GPIO及关中断寄存器,等待中断信号的来临。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章