资料下载

高速PCB电路板的信号完整性设计

高速PCB电路板的信号完整性设计

摘要: 描述了高速PCB电路板信号完整性设计方法。 介绍了信号完整性基本理论, 重点讨论了如何采用高速PCB设计方法保证高速数采模块的信号完整性,

关键词: 信号完整性; PCB设计;

集成电路芯片构成的电子系统朝着大规模、小体积、高速度方向发展, 信号的工作频率也不断提高, 使得PCB的布局布线密度变大, 输出开关速度过高, 引起信号延迟、时序问题及串扰、传输线效应等信号完整性问题, 从而导致系统工作不稳定, 甚至完全不工作。 因此, 如何在系统设计以及板极设计中考虑到信号完整性的因素, 并采取有效的控制措施, 成为一个设计成功的关键因素 。 文中在对信号完整性设计的基本理论做出一个完整的阐述。

1� 信号完整性基本理论

1. 1� 信号完整性定义

信号完整性( S igna l Integrity, S I)是指在信号线上的信号质量, 是信号在电路中能以正确的时序和电压做出响应的能力。 当电路中信号能以要求的时序、持续时间和电压幅度到达IC 时, 该电路就有很好的信号完整性。

1. 2� 影响信号完整性的主要因素

引起信号完整性问题的因素很多, 主要因素有延迟、反射、串扰、地弹以及电磁干扰。 信号时延主要表现为信号在逻辑电平的高、低门限之间变化时, 保持一段时间信号不跳变。 过多的信号延时可能导致时序错误和器件功能的混乱。 信号延时的原因包括驱动过载和走线过长。 传输时延与信号线的长度、信号传输速度。

反射, 即为传输线上的回波。 反射信号产生的主要原因是过长的走线、未被匹配终端的传输线、过量电容或电感及阻抗失配。 当一根信号线上有信号通过时, 在PCB 板上与之相邻的信号线上就会感应出相关的信号, 这种现象称之为串扰。 信号线距离地线越近, 线间距越大, 产生的串扰信号越小。 地弹是指当电路中有大的电流涌动时产生的地平面反弹噪声。 电磁干扰包括产生过量的电磁辐射及对电磁辐射的敏感性两个方面。 EM I产生的主要原因是电路工作频率太高及布局、布线不合理。

2� 高速数据采集系统

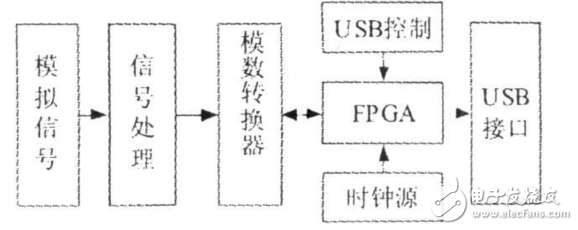

高速数据采集系统原理框图如图1所示, 此高速数据采集系统体积小巧轻便, 致使电路板布局布线密度高; 系统时钟运行频率为100MH z以上, ADC 芯片转换率在125MH z左右, 属于高速系统; 同时系统工作还需多种电源供电, 因此对其分析必须全面考虑信号完整性

。

图1� 数据采集系统原理框图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章