资料下载

×

HEVC中CABAC解码器的硬件设计与实现

消耗积分:0 |

格式:rar |

大小:1.16 MB |

2017-11-15

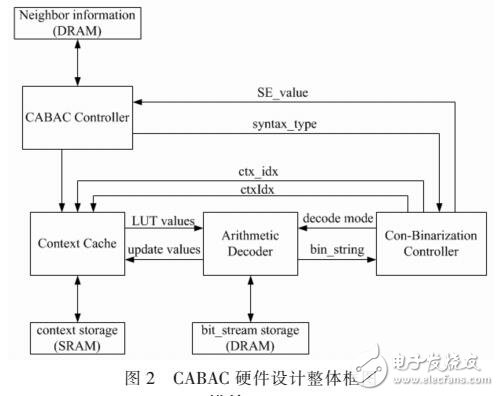

随着高清视频应用日益增加,对视频压缩性能提出了更高的要求。因此,2010年4月国际电信联盟电信标准化部门(IUT-T)的视频编码专家组(VCEG)和国际标准化组织(ISO)的动态图像专家组(MPEC)组建视频编码联合组(JCT-VC),联手制定了新一代视频编码标准HEVC。HEVC采用CABAC的熵编码方式,获得了高的压缩效率,但实现结构复杂,诸多的迭代运算,加上各级之间的相关特性使其很难并行化,在硬件实现上占用较多的面积并且速度较慢。

文中设计了一个高性能的CABAC解码器,通过对单周期解码1bit的结构进行改进,优化了面积和关键路径等特性,提高了解码性能。该设计采用Verilog HDL进行建模和仿真,并利用Synopsys公司的相关T具进行了面积和时序分析。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章