资料下载

×

曼彻斯特电压/电流编译码系统设计方案

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-11-27

由于曼彻斯特(MancheSTer)编码具有传输时无直流分量,时钟提取方便等特点,被广泛地应用于以太网、车辆总线、工业总线中。现在工程上常用的曼彻斯特编译码芯片为HD-6408和HD-6409,但是这种芯片有一些不足。首先,该芯片在传输速率和每帧数据中的有效位数等方面都做了严格的限制。其次,使用该芯片需要增加额外的硬件电路,提高了系统成本。使用FPGA做曼彻斯特编译码成本高,而且开发周期长。本文提出了一种基于STM32F103RET6的编译码系统方案,利用了STM32F103RET6强大的定时器功能,采用灵活的编译码方式,传输速率和数据帧格式都可以根据需要完全自行定义。STM32F103RET6自带DMA的功能使得数据编码不再需要频繁的定时中断,提高了编码速率,节约了CPU的资源。该设计方案实现方法简单、稳定、灵活,应用范围广泛。

1 曼彻斯特码

曼彻斯特编码是一种自动同步的编码方式即时钟同步信号就隐藏在数据波形中。在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作为时钟信号,又作为数据信号。每个码元均用两个不同相位的电平信号表示,与用高、低电平表示的非归零二进制码相比,在连“0”或连“1”的情况下更易于提取同步时钟信息。并且曼彻斯特码传输时没有直流分量,可以降低系统的功耗,且有很强的抗干扰能力。图1所示是最常用的一种曼彻斯特编码方法,当传送信号为“1”时,曼彻斯特编码由高电平跳变为低电平;若传送的信息为“0”,曼彻斯特由低电平跳变为高电平,在一个数据周期内保持低电平无跳变则表示空闲。

图1 曼彻斯特编码

2 STM32F103RET6的定时器与DMA简介

控制器采用ST公司的STM32微处理器,STM32系列微处理器基于ARM Cortex-M3内核,采用高效的哈佛结构三级流水线,达到1.25DMIPS /MHz,这里我们选用增强型的STM32F103RET6.它具有如下特征:72 MHz系统时钟频率、512 KB闪存程序存储器、64 KBSRAM、8个定时器、3个12位模数转换器、1个数模转换器,1个CAN接口、7通道DMA控制器,以及SPI、USART、I2C、I2S、USB接口等。该控制器具有丰富的外设和较强的抗干扰能力,很适用于工业现场控制。

STM32F103RET6有8个定时器,每个定时器由一个可编程预分频的1 6位自动装载计数器构成,计数频率高达72 MHz,它适用于多种场合包括输入信号的脉冲长度(输入捕获)或者产生输出波形(输出比较或者PWM)。

STM32F103RET6支持DMA操作,DMA是在外没和存储器之间或者存储器和存储器之间的高速数据传输通道,通过DMA数据可以快速地移动而无需CPU的参与,这就节省了CPU的资源来做其他事情。本次设计便是利用计数器触发DMA进行内存与定时器的数据交换,比起中断查询的方式,提高了编码的效率和稳定性。

定时器的计数频率最高为72 MHz,DMA传输速率为6 Mb/s,因此曼彻斯特编码的速率可以很轻松的做到1 Mb/s,满足高速编码的需求。

3 系统实现方案

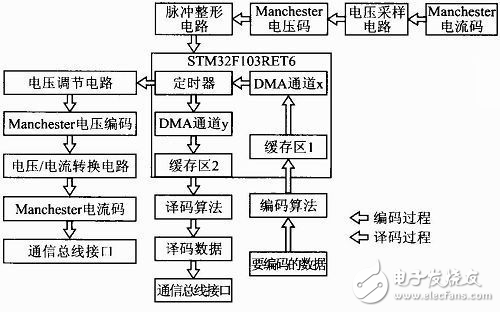

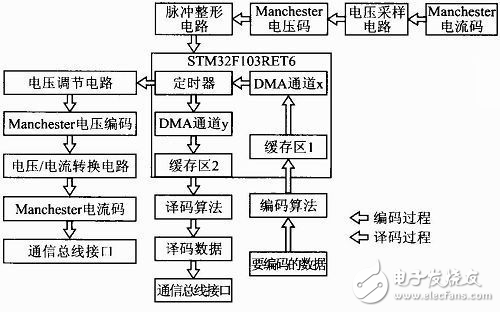

基于STM32F103RET6的曼彻斯特电压、电流编译码系统框图如图2所示。该系统设计主要使用STM32F103RET6芯片的定时器加DMA功能来实现曼彻斯特的电压编译码,对于电流编码译码需要借助外围的电压与电流转换电路来实现。

图2 基于STM32F103RET6的曼彻斯特电压、电流编译码系统框图

3.1 电压编码

将定时器设置为输出比较翻转功能,申请一个缓存区,将要编码的数据通过编码算法转换为翻转匹配值放入此缓存区,如图3所示的ABC DEF……计数值,编码算法根据具体应用中的编码协议来编写。启动定时器后,计数器开始计数,当计数值与定时器比较寄存器的值匹配时,输出引脚的电平进行翻转并触发DMA从缓存区来更新比较寄存器;每更新一次,DMA指向的内存地址递增1,指向下一次要更新到比较寄存器的数据,以此方式实现定时器根据缓存区的数据输出对应的编码波形。编码速率可通过修改定时器预分频器和RCC时钟控制器分频器来进行调节。

1 曼彻斯特码

曼彻斯特编码是一种自动同步的编码方式即时钟同步信号就隐藏在数据波形中。在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作为时钟信号,又作为数据信号。每个码元均用两个不同相位的电平信号表示,与用高、低电平表示的非归零二进制码相比,在连“0”或连“1”的情况下更易于提取同步时钟信息。并且曼彻斯特码传输时没有直流分量,可以降低系统的功耗,且有很强的抗干扰能力。图1所示是最常用的一种曼彻斯特编码方法,当传送信号为“1”时,曼彻斯特编码由高电平跳变为低电平;若传送的信息为“0”,曼彻斯特由低电平跳变为高电平,在一个数据周期内保持低电平无跳变则表示空闲。

图1 曼彻斯特编码

2 STM32F103RET6的定时器与DMA简介

控制器采用ST公司的STM32微处理器,STM32系列微处理器基于ARM Cortex-M3内核,采用高效的哈佛结构三级流水线,达到1.25DMIPS /MHz,这里我们选用增强型的STM32F103RET6.它具有如下特征:72 MHz系统时钟频率、512 KB闪存程序存储器、64 KBSRAM、8个定时器、3个12位模数转换器、1个数模转换器,1个CAN接口、7通道DMA控制器,以及SPI、USART、I2C、I2S、USB接口等。该控制器具有丰富的外设和较强的抗干扰能力,很适用于工业现场控制。

STM32F103RET6有8个定时器,每个定时器由一个可编程预分频的1 6位自动装载计数器构成,计数频率高达72 MHz,它适用于多种场合包括输入信号的脉冲长度(输入捕获)或者产生输出波形(输出比较或者PWM)。

STM32F103RET6支持DMA操作,DMA是在外没和存储器之间或者存储器和存储器之间的高速数据传输通道,通过DMA数据可以快速地移动而无需CPU的参与,这就节省了CPU的资源来做其他事情。本次设计便是利用计数器触发DMA进行内存与定时器的数据交换,比起中断查询的方式,提高了编码的效率和稳定性。

定时器的计数频率最高为72 MHz,DMA传输速率为6 Mb/s,因此曼彻斯特编码的速率可以很轻松的做到1 Mb/s,满足高速编码的需求。

3 系统实现方案

基于STM32F103RET6的曼彻斯特电压、电流编译码系统框图如图2所示。该系统设计主要使用STM32F103RET6芯片的定时器加DMA功能来实现曼彻斯特的电压编译码,对于电流编码译码需要借助外围的电压与电流转换电路来实现。

图2 基于STM32F103RET6的曼彻斯特电压、电流编译码系统框图

3.1 电压编码

将定时器设置为输出比较翻转功能,申请一个缓存区,将要编码的数据通过编码算法转换为翻转匹配值放入此缓存区,如图3所示的ABC DEF……计数值,编码算法根据具体应用中的编码协议来编写。启动定时器后,计数器开始计数,当计数值与定时器比较寄存器的值匹配时,输出引脚的电平进行翻转并触发DMA从缓存区来更新比较寄存器;每更新一次,DMA指向的内存地址递增1,指向下一次要更新到比较寄存器的数据,以此方式实现定时器根据缓存区的数据输出对应的编码波形。编码速率可通过修改定时器预分频器和RCC时钟控制器分频器来进行调节。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章