资料下载

×

一文看懂DDR布线背后的大学问

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-11-28

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制/命令信号与时钟做等长。数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时处理这些信号。那么,时钟信号和地址同时到达接收端,波形的对应关系是什么样的呢?我们通过仿真来看一下具体波形。

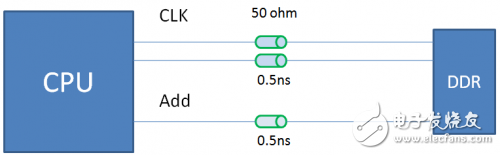

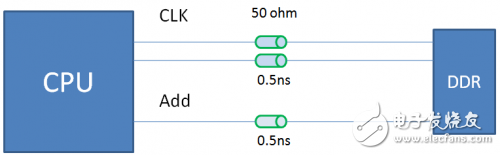

建立如下通道,分别模拟DDR3的地址信号与时钟信号。

图1 地址/时钟仿真示意图

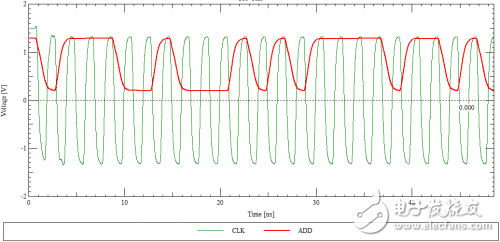

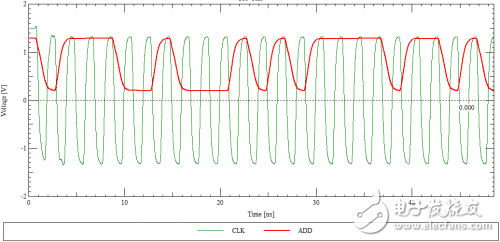

为方便计算,我们假设DDR的时钟频率为500MHz,这样对应的地址信号的速率就应该是500Mbps,这里大家应该明白,虽然DDR是双倍速率,但对于地址/控制信号来说,依然是单倍速率的。下面来看看波形,在地址与时钟完全等长的情况下,地址与数据端的接收波形如下图2,红色代表地址信号,绿色代表时钟信号。

图2 时钟信号与地址信号波形

建立如下通道,分别模拟DDR3的地址信号与时钟信号。

图1 地址/时钟仿真示意图

为方便计算,我们假设DDR的时钟频率为500MHz,这样对应的地址信号的速率就应该是500Mbps,这里大家应该明白,虽然DDR是双倍速率,但对于地址/控制信号来说,依然是单倍速率的。下面来看看波形,在地址与时钟完全等长的情况下,地址与数据端的接收波形如下图2,红色代表地址信号,绿色代表时钟信号。

图2 时钟信号与地址信号波形

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章