资料下载

×

多核DSP在军事应用中的实现

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-12-04

随着无人机(UAV)、声纳、雷达、信号情报(SIGINT)以及软件定义无线电(SDR) 等波形密集型应用中的信号处理需求不断攀升,多个数字信号处理器(DSP)内核的使用已成为重要的实现手段。多核功能与不断丰富的IP内核及开发工具相结合可实现优异的系统架构。所有这些应用都需要多核DSP来满足关键任务行业的各种需求,其中包括更强大的功能性(更快的处理速度)、更精细的分辨率以及更高的精度。过去,处理器性能的改善是通过工艺节点升级及提高运行时钟频率来实现的。然而,发展小型工艺节点和提高时钟频率并不是提高性能的低功耗捷径。在单个裸片中集成多核的这个方法可在更低的时钟频率及功耗下实现所需的高性能。

多核DSP以片上系统(SoC)形式设计,包含网络协处理器、安全加速器或FFT加速器等功能。为了满足军事应用的性能与成本需求,多核DSP应:

1. 支持混合执行引擎(内核)、矢量信号处理(VSP)以及更少的指令集计算(RISC);

2. 提供全面的多核优势,实现器件提供的全部功能;

3. 由一系列器件组成,支持缩放与重复使用。

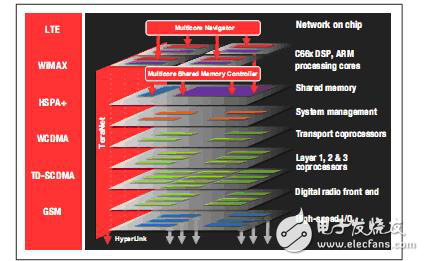

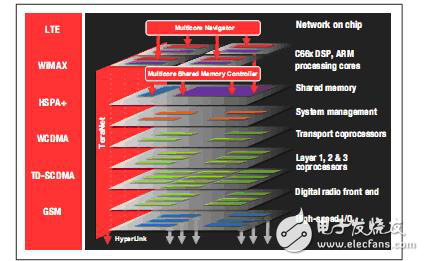

当前的多核器件或采用同质内核,即所有处理内核都是相同的;或采用异质内核,即器件由不同类型的内核组成。几乎所有应用都需要混合搭配的处理功能来满足行业需求。从开发人员角度看,重点是支持同质内核,因为异质系统架构可通过同质器件创建。反之,如果不牺牲性能就很难实现。图1(下图)是作为异质多核架构实例的德州仪器 (TI) KeyStone多核架构。

图1:德州仪器KeyStone多核架构

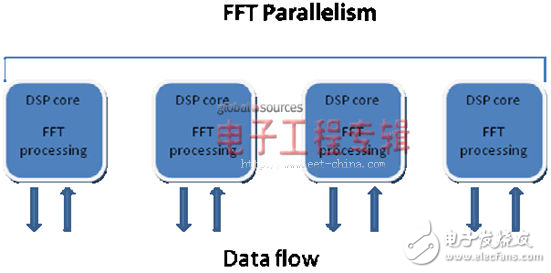

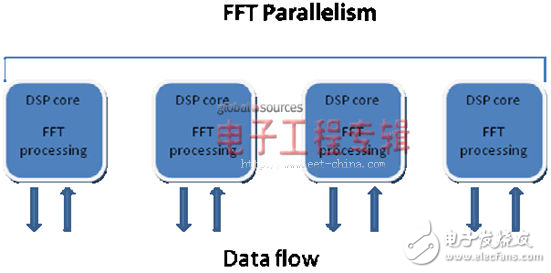

TI KeyStone多内核架构拥有高度的灵活性,可同时集成定点与浮点运算、定向协处理与硬件加速,以及优化的内核间/组件间通信。此架构包括多个 C66x DSP 内核,能够支持高达 256 GMAC 的定点运算性能以及 128GFLOP 的浮点运算性能。另外,此架构还包括综合而全面的连接功能层:TeraNet2 能够与各种处理组件无缝互连;多内核共享内存控制器能直接接入片上共享存储器与外部第三代双倍数据速率 (DDR3) 存储器;多内核导航器可助于管理整个 SoC 架构的通信;以及 HyperLink 50 可与额外的协处理器或其他 TI SoC 等同伴器件实现互通互连。部分此类关键处理组件可在 TI SoC 上实现 LTE L2 与传输处理。多核DSP支持的并行处理功能可为要求严格的军事应用提供重要功能。雷达要求更快的FFT响应时间,根据FFT要求,开发人员可使用器件中的所有内核或部分内核满足FFT的实施需求。如果FFT的性能使用部分内核即可实现,其它DSP内核则可执行系统中的信号预处理或后处理,或者其它任务。图2所示即为并行FFT示例。采用可充分发挥多核优势的软件工具可为正在进行的设计判定最佳内核配置(内核数量)。这样开发人员就可高度灵活地满足多重应用需求。

图2:4 DSP并行FFT实施

多核DSP目前正处于快速发展阶段。德州仪器等半导体公司提供的最新多核DSP采用通用架构,不但可帮助开发人员重复使用软件,而且还可为设备制造商节省开发时间。多核DSP正在成为声纳、雷达、SIGINT以及SDR应用的主要差异化因素,并正在为当前及未来信号处理系统实现令人振奋的全新系统开发。

多核DSP以片上系统(SoC)形式设计,包含网络协处理器、安全加速器或FFT加速器等功能。为了满足军事应用的性能与成本需求,多核DSP应:

1. 支持混合执行引擎(内核)、矢量信号处理(VSP)以及更少的指令集计算(RISC);

2. 提供全面的多核优势,实现器件提供的全部功能;

3. 由一系列器件组成,支持缩放与重复使用。

当前的多核器件或采用同质内核,即所有处理内核都是相同的;或采用异质内核,即器件由不同类型的内核组成。几乎所有应用都需要混合搭配的处理功能来满足行业需求。从开发人员角度看,重点是支持同质内核,因为异质系统架构可通过同质器件创建。反之,如果不牺牲性能就很难实现。图1(下图)是作为异质多核架构实例的德州仪器 (TI) KeyStone多核架构。

图1:德州仪器KeyStone多核架构

TI KeyStone多内核架构拥有高度的灵活性,可同时集成定点与浮点运算、定向协处理与硬件加速,以及优化的内核间/组件间通信。此架构包括多个 C66x DSP 内核,能够支持高达 256 GMAC 的定点运算性能以及 128GFLOP 的浮点运算性能。另外,此架构还包括综合而全面的连接功能层:TeraNet2 能够与各种处理组件无缝互连;多内核共享内存控制器能直接接入片上共享存储器与外部第三代双倍数据速率 (DDR3) 存储器;多内核导航器可助于管理整个 SoC 架构的通信;以及 HyperLink 50 可与额外的协处理器或其他 TI SoC 等同伴器件实现互通互连。部分此类关键处理组件可在 TI SoC 上实现 LTE L2 与传输处理。多核DSP支持的并行处理功能可为要求严格的军事应用提供重要功能。雷达要求更快的FFT响应时间,根据FFT要求,开发人员可使用器件中的所有内核或部分内核满足FFT的实施需求。如果FFT的性能使用部分内核即可实现,其它DSP内核则可执行系统中的信号预处理或后处理,或者其它任务。图2所示即为并行FFT示例。采用可充分发挥多核优势的软件工具可为正在进行的设计判定最佳内核配置(内核数量)。这样开发人员就可高度灵活地满足多重应用需求。

图2:4 DSP并行FFT实施

多核DSP目前正处于快速发展阶段。德州仪器等半导体公司提供的最新多核DSP采用通用架构,不但可帮助开发人员重复使用软件,而且还可为设备制造商节省开发时间。多核DSP正在成为声纳、雷达、SIGINT以及SDR应用的主要差异化因素,并正在为当前及未来信号处理系统实现令人振奋的全新系统开发。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章