资料下载

×

SoC存储器的智能电源连接方法

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-12-06

简介

SoC设计也面临着一系列的难题和挑战,其中出现的最大挑战之一是硬核IP模块集成和验证。随着技术的扩展,设计并集成IP模块变得越来越难。在深亚微米技术设计中,IR压降往往会对功能性造成显著的影响。

本文介绍了一种新的IR压降方法,使用这种方法可以带来非常稳健的内部电网结构。凭借强大的设计技术,该IR压降方法能带来出色的硅结果,单端口高速RAM上的8Kx72切口最低电压可低至0.52V。

存储器基本架构

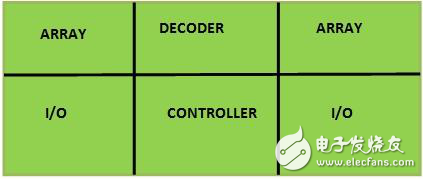

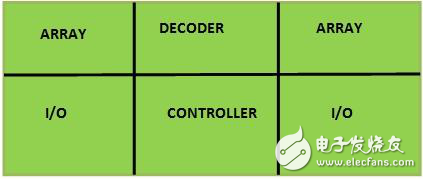

存储器通常包含四个基本模块——控制器、解码器、阵列比特单元和输入/输出端。大部分吸收较多电流的大型驱动器都被置于输入/输出端、解码器和控制模块中。因此,为使各模块正常运作,我们需要确保每个驱动器有足够的电压来保证正常运行。

存储器基本模块图图1:存储器基本模块图

图字:阵列;解码器;阵列;输入/输出端;控制器;输入/输出端

系统芯片存储器的连接指南

1.一般方法

一般地,存储器所有者会以电网的捆扎频率的形式向设计电源连接的SoC设计人员提供所有电源轨的指导大纲。捆扎频率定义了给定电源线上的两个连续金属带(一般在顶端金属)之间的距离。在建造电网时按照捆扎指导大纲操作,可确保几乎所有驱动器可获得足够的工作电压,实现良好的性能。

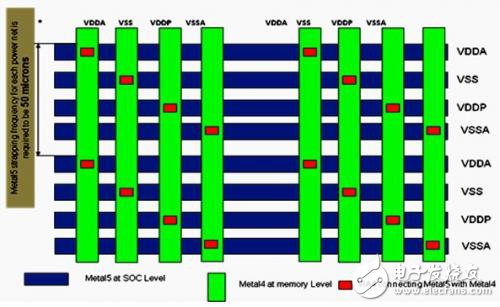

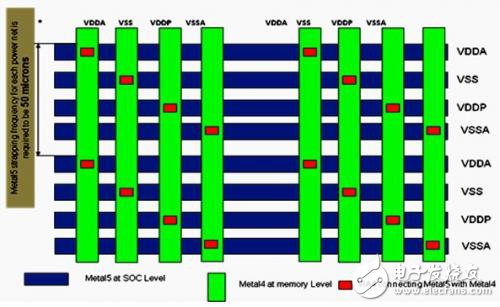

在图2中,M4的供电轨是垂直的,应与水平的M5相连接。目标存储器中存在着多个电源域,如VSSA、VDDP、VSS和VDDA等等。

图2:系统芯片的电源连接结构图

图字:要求每个电源网的金属5捆扎频率为50微米;系统芯片级金属5;存储器级金属4;VIA4将金属5与金属4相连接

将捆扎频率作为唯一决定因素会导致的问题

假设对于某项特定的技术,规定了一个50um的捆扎频率。也就是说,每隔50um就应当重复电源线以确保恰当的功能和输出。在这种情况下,只有一个电源线的驱动(VDD、VSS)是受IR压降影响最严重的,因此这些装置可能会出现异常行为。

在图3中,分频器3和分频器1只分到一根VDD/VSS电源线,因此可能无法获得足够的电压来确保正常的运作。此处,分频器2有多个电源线,因而可以正常运行。

在单块存储器中,仅仅使用strapping技术也许足以确保正常的运行。然而,对于多组架构的储存器或较长、较宽的存储器而言,仅仅使用strapping技术是不足以实现IR压降要求的。因此,在这种情况下,除了strapping之外,我们还需要使用其他方法来帮助我们实现IR的压降目标。

SoC设计也面临着一系列的难题和挑战,其中出现的最大挑战之一是硬核IP模块集成和验证。随着技术的扩展,设计并集成IP模块变得越来越难。在深亚微米技术设计中,IR压降往往会对功能性造成显著的影响。

本文介绍了一种新的IR压降方法,使用这种方法可以带来非常稳健的内部电网结构。凭借强大的设计技术,该IR压降方法能带来出色的硅结果,单端口高速RAM上的8Kx72切口最低电压可低至0.52V。

存储器基本架构

存储器通常包含四个基本模块——控制器、解码器、阵列比特单元和输入/输出端。大部分吸收较多电流的大型驱动器都被置于输入/输出端、解码器和控制模块中。因此,为使各模块正常运作,我们需要确保每个驱动器有足够的电压来保证正常运行。

存储器基本模块图图1:存储器基本模块图

图字:阵列;解码器;阵列;输入/输出端;控制器;输入/输出端

系统芯片存储器的连接指南

1.一般方法

一般地,存储器所有者会以电网的捆扎频率的形式向设计电源连接的SoC设计人员提供所有电源轨的指导大纲。捆扎频率定义了给定电源线上的两个连续金属带(一般在顶端金属)之间的距离。在建造电网时按照捆扎指导大纲操作,可确保几乎所有驱动器可获得足够的工作电压,实现良好的性能。

在图2中,M4的供电轨是垂直的,应与水平的M5相连接。目标存储器中存在着多个电源域,如VSSA、VDDP、VSS和VDDA等等。

图2:系统芯片的电源连接结构图

图字:要求每个电源网的金属5捆扎频率为50微米;系统芯片级金属5;存储器级金属4;VIA4将金属5与金属4相连接

将捆扎频率作为唯一决定因素会导致的问题

假设对于某项特定的技术,规定了一个50um的捆扎频率。也就是说,每隔50um就应当重复电源线以确保恰当的功能和输出。在这种情况下,只有一个电源线的驱动(VDD、VSS)是受IR压降影响最严重的,因此这些装置可能会出现异常行为。

在图3中,分频器3和分频器1只分到一根VDD/VSS电源线,因此可能无法获得足够的电压来确保正常的运作。此处,分频器2有多个电源线,因而可以正常运行。

在单块存储器中,仅仅使用strapping技术也许足以确保正常的运行。然而,对于多组架构的储存器或较长、较宽的存储器而言,仅仅使用strapping技术是不足以实现IR压降要求的。因此,在这种情况下,除了strapping之外,我们还需要使用其他方法来帮助我们实现IR的压降目标。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章