资料下载

×

MPPSK数字接收机位同步算法设计与实现

消耗积分:2 |

格式:rar |

大小:3.43 MB |

2017-12-21

随着社会技术和经济的发展,迫切希望能实现多媒体数据高速传输,因而现代通信系统带宽不断增加,随之而来的是无线频谱资源的紧缺。高效调制技术能在单位时间内传输更多的信息,同时占用更窄的频带,因此研究高效调制技术具有重大的意义。

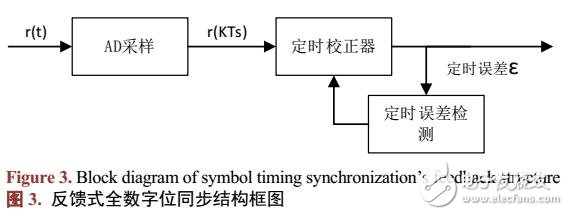

位同步又称码元同步,是数字通信接收机的重要组成部分。发端的消息是通过一连串码元序列传送的,接收时需要知道每个码元的起始,以便在恰当的时刻进行取样判决。所以接收端必须提供一个位定时脉冲序列,其重复频率与码元速率相同,相位与最佳取样判决时刻一致,提取这种定时脉冲序列的过程称为位同步。

本文首先介绍MPPSK调制与解调原理,再介绍数字接收机中的位同步系统。在分析传统算法后提出双窗实时位同步算法,介绍其实现结构,定时误差占的计算和具体算法的实现流程。最后利用FPGA开发环境System Generator系统设计工具进行设计和仿真,介绍算法的具体Verilog实现,并与数字接收机系统联调,验证算法性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章

下载排行榜

- 暂无相关数据