资料下载

×

一种双向环路冗余传输方案

消耗积分:1 |

格式:rar |

大小:1.78 MB |

2018-04-03

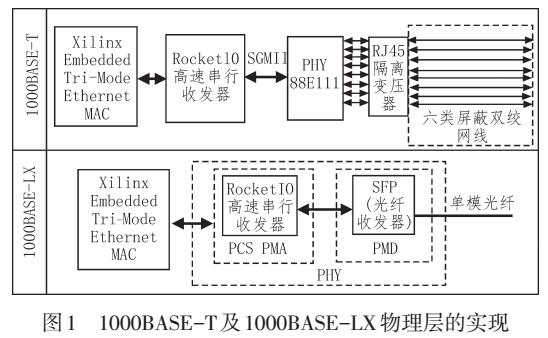

针对拖线阵声纳大规模发展带来的高速数据实时传输需求,借助Xilinx FPGA平台将千兆以太网传输技术应用于传输系统设计中。同时考虑到传输节点属水下核心工作模块,工作可靠性要求高,提出一种双向环路冗余传输方案,以赋予传输系统一定的容错工作性能。设计以FPGA芯片为核心,利用内嵌的以太网MAC控制器硬核,结合物理层PHY芯片完成了传输控制单元的开发,并利用Verilog语言开发了基于双重乒乓切换机制的数据处理模块,方便多个传输控制单元间进行数据帧的流水级转发。测试结果表明,链路的数据传输速率稳定在500 Mbps以上,并且能够实现对故障节点的隔离,具有容错工作性能。传输系统高效可靠,已用于某型拖线阵声纳系统试样阶段的研制。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章