资料下载

数字集成电路设计入门的Verilog详细中文资料概述

• 介绍Verilog HDL, 内容包括:

– Verilog应用

– Verilog语言的构成元素

– 结构级描述及仿真

– 行为级描述及仿真

– 延时的特点及说明

– 介绍Verilog testbench

• 激励和控制和描述

• 结果的产生及验证

– 任务task及函数function

– 用户定义的基本单元(primitive) – 可综合的Verilog描述风格

• 介绍Cadence Verilog仿真器, 内容包括:

– 设计的编译及仿真

– 源库(source libraries)的使用

– 用Verilog-XL命令行界面进行调试

– 用NC Verilog Tcl界面进行调试

– 图形用户界面(GUI)调试

– 延时的计算及反标注(annotation)

– 性能仿真描述

– 如何使用NC Verilog仿真器进行编译及仿真

– 如何将设计环境传送给NC Verilog

– 周期(cycle)仿真

• 逻辑综合的介绍

– 简介

– 设计对象

– 静态时序分析 (STA)

– design analyzer环境

– 可综合的HDL编码风格

• 可综合的Verilog HDL

– Verilog HDL中的一些窍门

– Designware 库

– 综合划分

• 实验 (1)

• 设计约束( Constraint)

– 设置设计环境

– 设置设计约束

• 设计优化

– 设计编译

– FSM的优化

• 产生并分析报告

• 实验 (2)

• 自动布局布线工具(Silicon Ensemble)简介

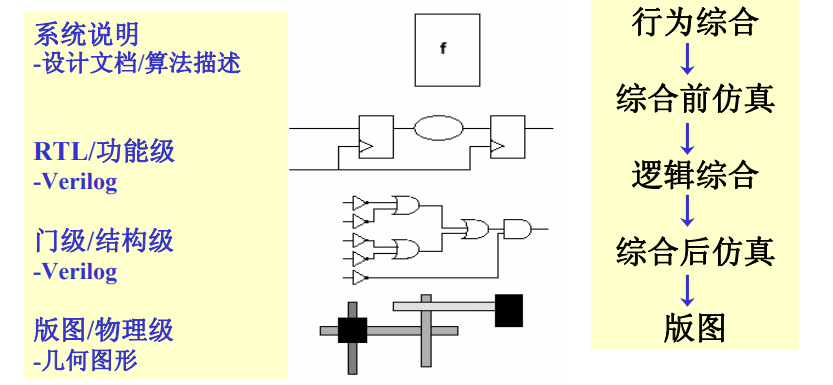

Verilog既是一种行为描述的语言也是一种结构描述语言。Verilog模型可以是实际电路的不同级别的抽象。这些抽象的级别包括:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章