资料下载

如何使用FPGA设计数字幅频均衡功率放大器详细资料说明

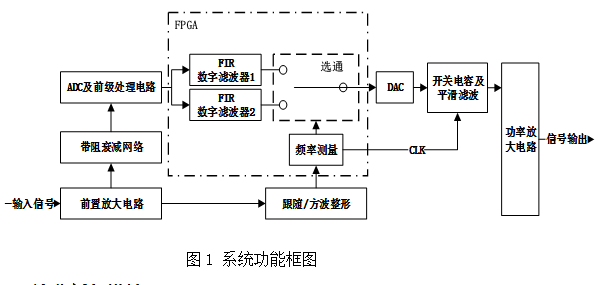

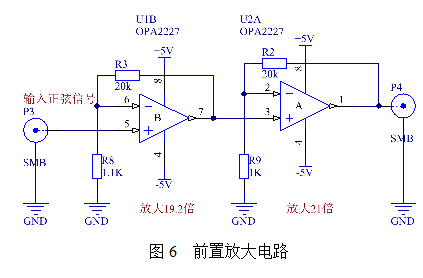

本系统是采用FPGA来设计的数字幅频均衡功率放大器,主要包括前置放大电路、带阻衰减网络、数字幅频均衡和音频功率放大电路四个模块构成。前置电路采用两级放大电路组成,放大倍数大于400倍。通过反复调整带阻衰减网络的参数,使其达到题目的要求。通过MATLAB工具设计出与带阻衰减网络相对应的一个带通FIR滤波器,并根据返回的系数将该滤波器在FPGA中实现,最终实现了幅频均衡。功率放大部分采用“集成运放+MOSFET”的组合模式,设计了一个CLASS-AB功率放大器。为了更好地实现幅频均衡,本设计采用了分段的方式进行均衡,即通过降采样的方式降低了滤波器的阶数要求。测试表明,本系统能实现幅频均衡,满足系统基本要求和发挥功能要求。

方案一:本题要求的输入信号频率在音频段20Hz~20KHz范围,经带阻网络后对信号进行采样, FFT算法分析信号的频率成分,然后根据带阻网络的幅频特性在频域对幅频特性进行补偿,在频域进行均衡。然后经过IFFT还原为时域信号,其优点是可采用DSP处理器完成FFT和IFFT算法,实现方便。缺点是难以兼顾频率分辨率、频率分析范围和分析时间要求,而且DSP成本较高。

方案二:带阻网络输出信号经采样后,采用yulewalk函数设计IIR数字滤波,在时域进行均衡。根据yulewalk函数返回的IIR滤波器系数,在MATLAB Simulink组件中通过调用Altera 公司提供的DSP Builder库来构建一个IIR滤波器系统,最后在Quatus II中调用生成的HDL代码,将该数字滤波器配置到FPGA中。该方案的优点在于能够使用较低的阶数而达到理想的幅频均衡,这不仅降低了系统资源的消耗,而且还降低了工作量。但是IIR滤波器本身存在着非线性相位跟稳定性的问题,所以在音频处理中并不常用。

方案三:带阻网络输出信号经采样后,采用fir2(任意滤波器)函数设计FIR数字滤波,在时域进行均衡。为了降低FIR滤波器的阶数要求,我们将20˜20kHz信号分成两段均衡,针对这两个频率段的信号采用不同的采样率进行采样,通过MATLAB工具分别设计出不同采样率对应的FIR滤波器。最后根据返回的滤波器系数,调用Quatus II中FIR Compiler II IP核设计出两个并行处理的FIR滤波器,实现幅频均衡。由于Quatus II中有现成的FIR IP核可以调用,使用该方案可以大大缩短开发周期、提高效率,而且FIR滤波器本身具有线性相位跟稳定性的优点。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章