资料下载

如何使用隔离设计流程与Spartan-6系列开发安全的FPGA设计

本应用说明是为希望使用Xilinx®隔离设计流程(IDF)实现安全性或关键性设计的FPGA设计人员编写的,例如信息保证(单芯片加密〔SCC〕、航空电子、汽车和工业应用。本文档说明了如何:

•在单个spartan®-6或spartan-6q(国防级)fP中使用IDF实现隔离功能,例如红/黑逻辑、冗余的I型加密模块或逻辑处理多个安全级别。

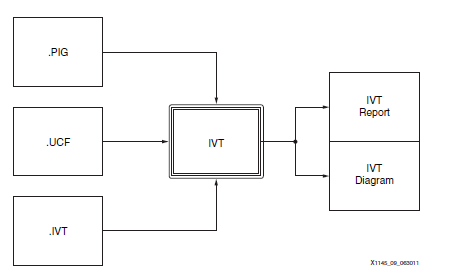

•使用Xilinx隔离验证工具(IVT)验证隔离。

根据此应用说明,设计人员可以使用IDFTHAT开发一个故障安全的单芯片解决方案,以满足高级别、高保证应用的故障安全和物理安全要求。为了增加设计的安全性,可以购买由Xilinx开发的安全监视器IP。要嵌入此IP,必须按照SPARDAN-6 FPGA安全监视器2.0集成和验证中的说明修改本文档中的步骤。更多信息,请联系您当地的Xilinx代表。

如果目标应用程序是1类加密应用程序(即SCC应用程序),则必须选择防御级(XQ)设备。

可编程逻辑的灵活性为安全和安全关键行业提供了许多优势。然而,在这项工作之前,在信息保障等应用中,由于隔离、可靠性和安全问题,政府承包商和机构无法实现可编程逻辑的全部能力。为了解决这些问题,开发了IDF以允许独立功能在单芯片(SCC)上运行。此类SCC应用程序的示例包括但不限于冗余的I型加密模块、驻留的红色和黑色数据以及在多个独立安全级别上运行的功能。这项工作的成功完成使Xilinx能够为信息保障行业提供新技术,并在航空电子、汽车和工业应用中提供安全关键功能。

通过Xilinx分区技术和部分重新配置(PR)许可证,可以在单个FPGA中开发一个包含多个隔离功能的安全的单芯片解决方案。虽然spartan-6 FPGA不支持PR,但许可证及其功能必须提供控制,以实现满足认证机构要求所需的隔离。为了更好地理解IDF的细节,设计者应该对标准分区设计流程有一个扎实的理解。IDF中使用了分区流中的许多术语和过程。不同的区域将取代分区设计流程,并在此应用程序说明中标识。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章