资料下载

使用FPGA平台的处理器ARMCortex原型设计的说明

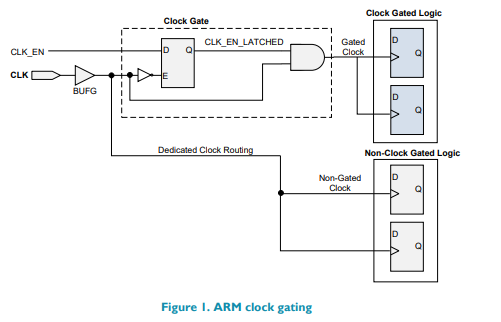

随着新型SoC(片上系统)设计的成本和复杂性的不断提高,现场可编程门阵列(FPGA)原型技术正日益成为SoC新项目的重要组成部分,甚至是至关重要的组成部分。通过提供一种更快到达硬件的方法,FPGA原型设计允许硬件验证和软件工作更早地开始,在第一个硅之前,有效地流水线设计过程。现代可重新编程的FPGA是灵活多样的计算和原型平台-易于重新配置开发系统以测试总体设计中的连续过程,这为开发人员提供了一个主要优势,并在承诺生产成本高昂的ASIC之前对设计充满信心。在FPGA中的原型设计也允许调试和可观察性技术,否则将不可用,例如直接在FPGA结构中插入信号探针。然而,通过将SOC实现到FPGA中实现原型,确实存在一些需要考虑的独特挑战。在将SOC设计映射到FPGA上时,底层的FPGA架构和资源提供了限制和可能性。

在FPGA中,几乎不可能达到所实现的IP在硅中的预期速度。由于各种因素(如插针多路复用),多FPGA设计中的最大频率传统上被限制在远低于FPGA结构限制的速度。

在过去,由于ARM内核更小,系统也不那么复杂,通常可以将整个系统安装到单个FPGA上。目前,即使考虑到现代FPGA平台上可用的容量和各种资源的大幅增加,以及当前对更强大的应用处理器和更大的ASSP的需求,构成一个系统的所有构建块可能并不总是适合于一个FPGA,即使在商业上使用最大的FPGA也是如此。书写时贴上标签。因此,有时有必要将设计分解成更小的块,并将它们安装到几个连接的FPGA中。这就提出了如何在多个FPGA上对系统或设计进行最佳分区的附加问题。

在本白皮书中,我们讨论了ARMCortex(使用FPGA平台的类处理器)原型设计时遇到的常见问题。我们展示了如何将ARM处理器IP应用于FPGA中的实现,并给出了如何在多个FPGA中对系统进行分区的指导原则。FPGA平台、板和工具因供应商和版本而异。对于这些文件和支持,建议直接联系相关供应商。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章