资料下载

运算放大器和DAC及ADC高速数据转换的详细资料说明

在很多方面,高速数据转换设计需要考虑的问题与一般数据转化十分相似,但由于芯片型号的限制,加上只有可靠的设计技术和结构才能使用,高速电路就显得有些不同,然而它们的基础是一样的。 高速电路或系统往往促进了前沿技术动态性能的发展。

这篇报告主要集中介绍了基本模块如运算放大器,采样/保持,数模转换和模数转换器(DAC & ADCDACsand ADCs),本文以技术测试作为结束。作为系统基础的组件模块的运算放大器应该首先就要考虑,接下来需要考虑的是在数据转换中发挥重要作用的采样/保持,然后是DACs,最后ADCs, ADCs混合了以上三个电路。实际操作中,应特别强调混合及整体设计技术,因为这些操作直接影响到系统的最优性能。所用电路材料在进行设计之前就必须存在,同时这方面还应该有一定的理论与实践的例子,以便于数据转换设计者及使用者都可以找到有用的材料。现有的概念不要求设计者具有广泛的数据转换经验,下面讨论的基础观点很容易理解,文章着重强调高速电路设计时需要考虑的问题,对电路理论涉及不深。

放大器结构

所有的放大器在数据转换系统中占据着重要的地位。高速放大器很有用,但也很难设计,因此懂得它的工作原理就显得尤为重要。本文讨论了4种不同的放大器结构。信号处理器件中,比较常见的放大器有:缓冲器,运算放大器,开环放大器,比较器。

缓冲器

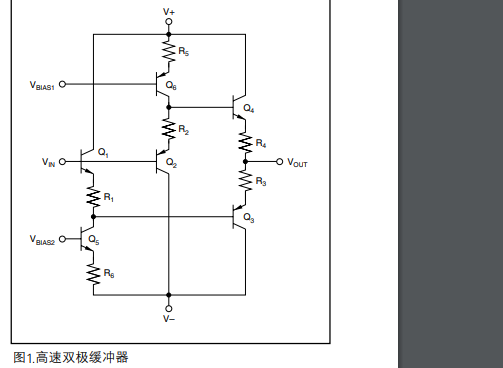

开环缓冲器是射极输出放大器中比较常见的一种结构。这种电路之所以受欢迎是因为它结构简单,功耗低,频带宽和易于使用。开环缓冲器在高速系统中占有很重要的地位。低速电压输出跟随器系统中,开环放大器的作用是一样的。该器件经常用于宽带运算放大器和其他类型的宽带放大器的输出中。如图1、2所示,给出了两种缓冲器电路的结构。每个缓冲器的输出阻抗大约是50,带宽位几百兆赫兹。FET缓冲器经常作为宽带FETS用在混合结构中。同时,同一单片电路工艺的晶体管不是都一样的。这种双极的缓冲器在单片电路中起到互补的作用,这里NPN和PNP晶体管都是有着很高性能的纵向结构。图1给出了这种缓冲器的一般结构。这个缓冲器的输入连接到一对互补的晶体管上。通过电阻R,和R,的输入晶体管连接到输出晶体管Q。和O。的基极,这样的话,如果基极到NPN和PNP的发射极电压相等的话,那么偏移量将为零。在相同的偏置电流下,如果将晶体管设计成具有相同Ve的几何尺寸时,就可以获得零偏移。当电路有合适的高输入阻抗和有高电流输出的能力时,那么这个电路是比较理想的。这种缓冲电路的一个重要应用是放大单片电路上运放的输出电流。单片电路上的运放通常没有超过10mA到50mA的输出电流,而如图一所示的缓冲器可以输出超过100mA的电流。这种缓冲器典型的带宽是250MHz,因此它可以应用于大多数单片运放的反馈环路中,且对稳定性的影响很小。图3给出的是一个缓冲器如何连接形成一个环路,这样放大器的DC性能就由无缓冲放大器和无输出缓冲器决定。图3给出的是这种连接的结构,缓冲器里存在驱动负载热耗散,这样的话就可以从敏感的运放的输入端减少热致的变形和补偿漂移。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章