几种低相位噪声信号生成方法

如何实现低BER(误码率)、低杂散输出和低相位噪声的系统级目标

Altera Cyclone V FPGA器件可实现降低设计系统成本和功耗

点频信号源由哪三部分组成?

担心STM32时钟PLL各参数配错吗?

ADI提供的完整5G基站信号链

频率规划技术可消除频谱中的干扰杂散信号

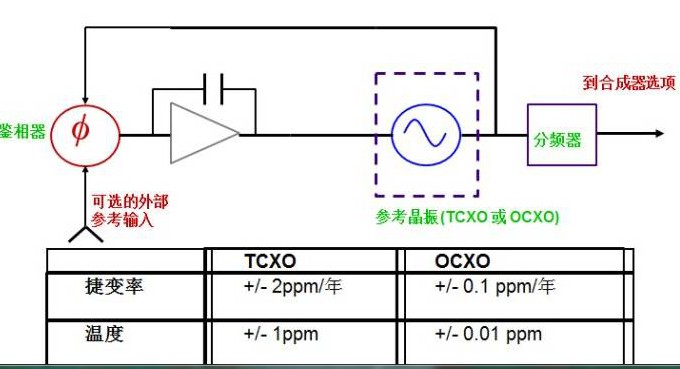

小数N分频锁相环频率合成器的介绍

琐相环的基本原理及应用范围

ADISimPLL锁相环电路设计和评估工具的应用

ADIsimPLL仿真工具支持ADI公司的PLL频率合成器系列

ADI的毫米波5G基地台信号链

高性能RF PLL和PLL VCO技术的介绍

全数字锁相环 (ADPLL)设计

大普通信新推出的高性能PLL芯片,支持任一频率转换及多路输入输出

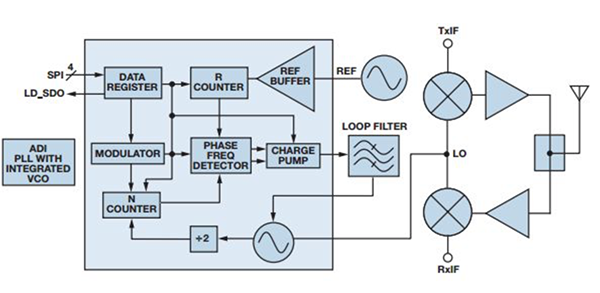

ADI公司集成VCO的PLL频率合成器改善基站性能和无线服务质量

Mouser备货Analog Devices公司最高频率PLL

可编程PLL硅时钟提供一流抖动性能

可再配置PLL的最佳配置

ADI推出4GHz PLL合成器具领先相位杂讯性能