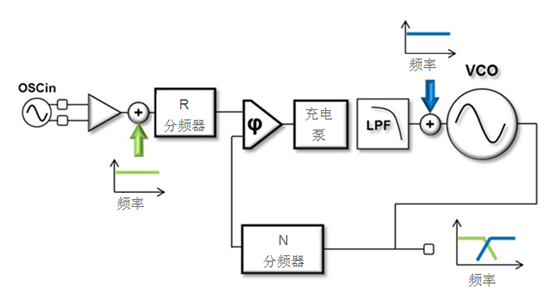

pll锁相环倍频的原理

HMC700LP4E PLL频率合成器典型应用

ADP7102ACPZ-3.3-R7 20 V、300 mA低噪声CMOS LDO

芯灵通科技自行研发PLL时钟电路芯片,助力小基站全国产化!

ADM7150 800 mA、超低噪声/高 PSRR LDO

pll是什么意思_pll锁相环参数

pll锁相环倍频

咨询应用工程师:PLL频率合成器

锁相环PLL的基础知识

PLL 时钟合成器模块CKM151 EUVIS

晶振在芯片中的作用

PiCO核心点—对比学习引入PLL

小编科普一下关于锁相环的一些概念

AD9528芯片介绍及配置详解

定时决定一切:如何使用部分PLL创建调制波形

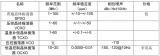

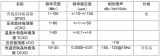

如何根据基本的数据表规格估算出PLL的相位噪声

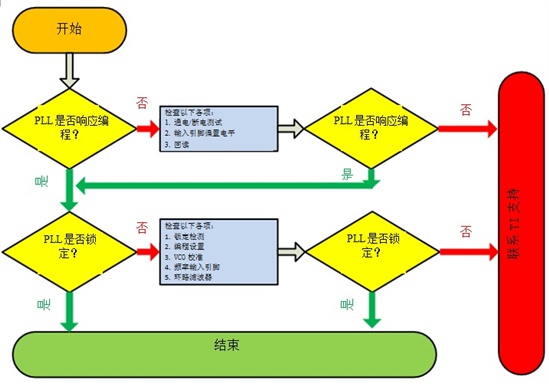

教大家如何解决锁相环无法锁定

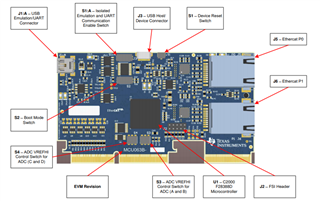

基于F28388的Ethercat Demo介绍

PLL芯片接口方面最常见的问题

PLL芯片接口方面最常见的11个问题