分立式ARM+FPGA与ZYNQ SoC相比,有哪些好处?

如何解决FPGA引脚与LVDS信号相连时兼容性的问题

基于Virtex-5 LX110验证平台实现FPGA性能的硬件系统设计

通过HLS封装一个移位流水灯的程序案例

DDR3 SDRAM控制器IP核的写命令和写数据间关系讲解

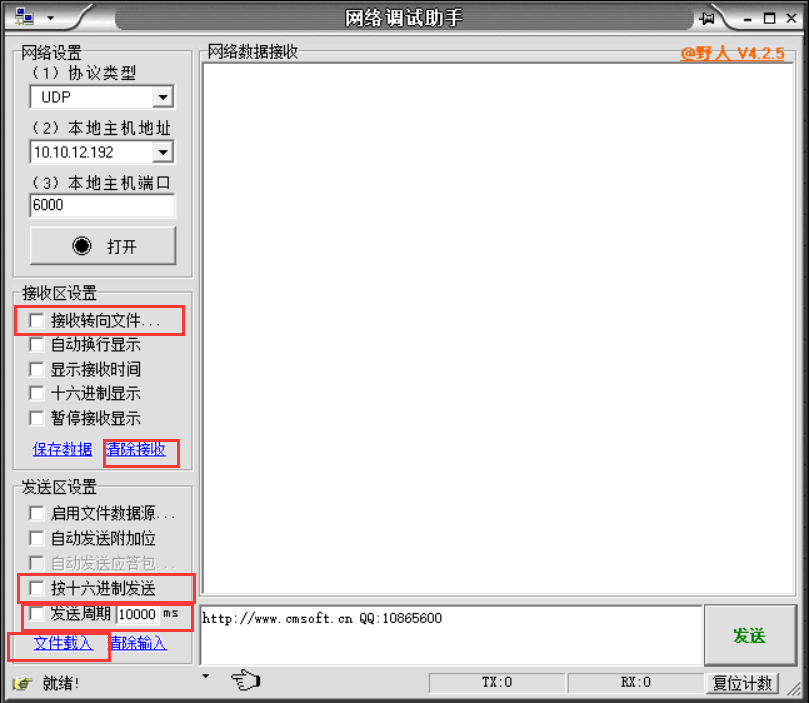

ZYNQ SOC案例开发:网络调试助手+W5500协议栈芯片

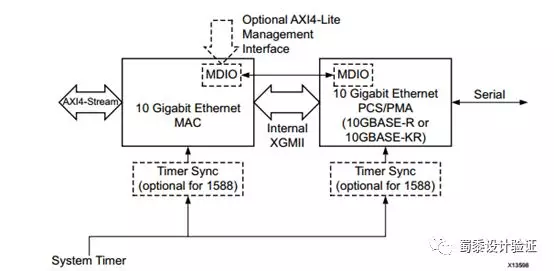

Xilinx Ten Giga Sub System IP生成详细步骤

基于FPGA的ASIC协同原型验证设计方案

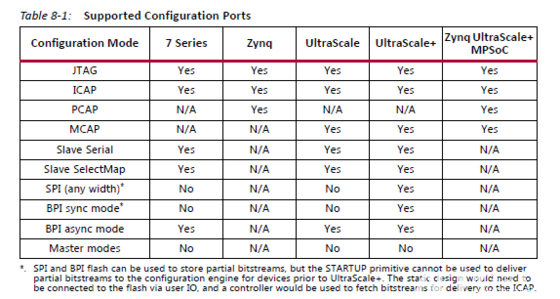

基于PCIE(mcap)的部分可重构实现方案

FPGA实现基于Vivado的BRAM IP核的使用

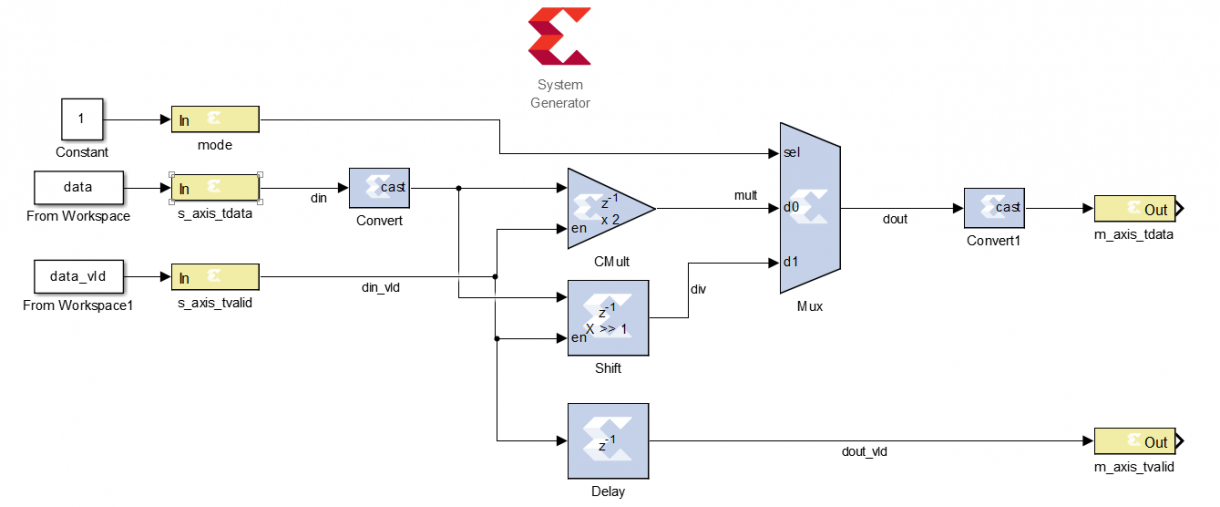

AXI总线实时配置sysGen子系统仿真实验

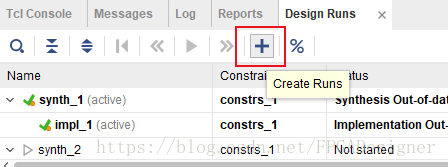

Vivado使用技巧分享:OOC综合技术运行流程

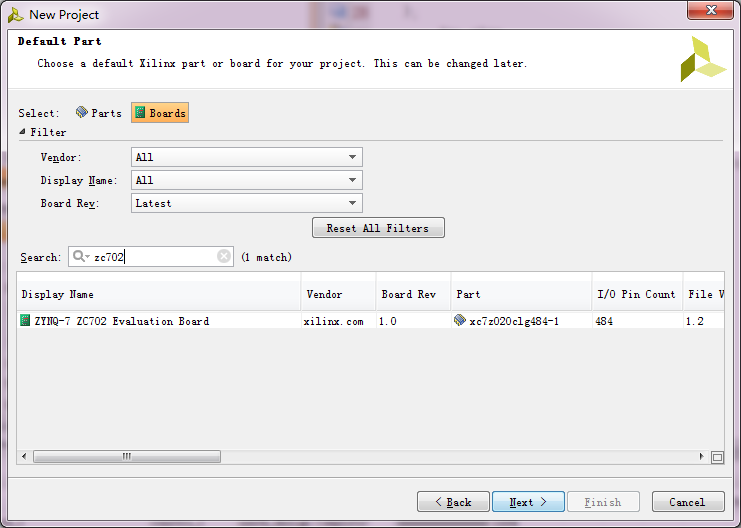

Xilinx ZYNQ开发案例HelloWorld实验工程

PCIE通信技术:通过AXI-Lite ip配置的VDMA使用

ZYNQ EMIO重用封装实现算法板级验证

Xilinx ZYNQ开发GPIO的三种方式:MIO、EMIO、AXI_GPIO

Linux + Xenomai实时操作系统创建方案

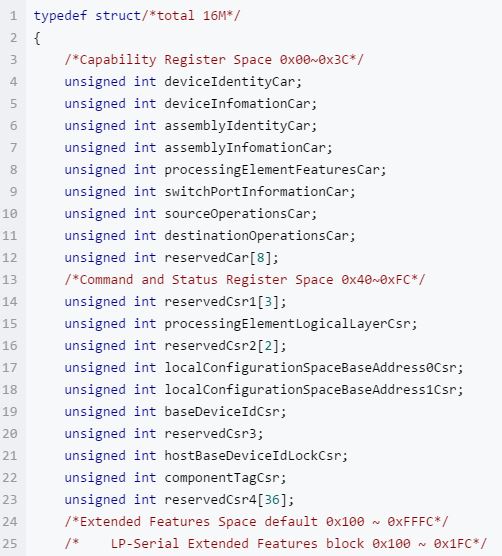

xilinx zynq RapidIO系统的初始化启动过程概述

ARM+FPGA开发:基于AXI总线的GPIO IP创建

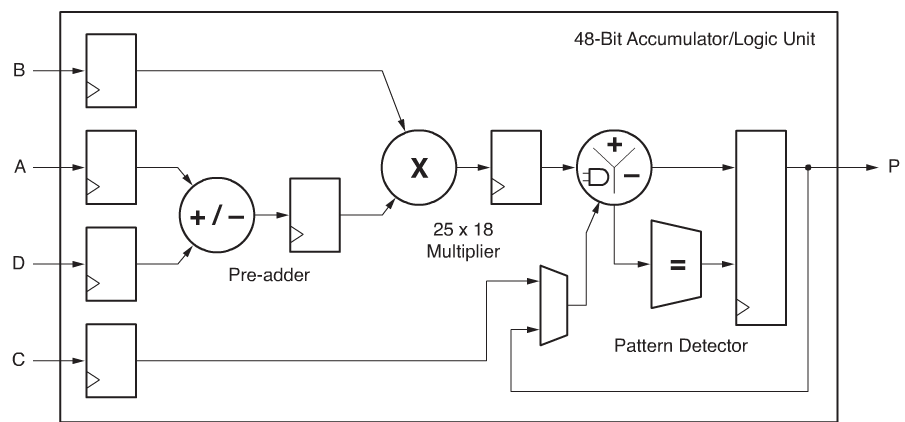

基本数学运算在FPGA中的实现算法仿真分析