资料下载

×

详解FPGA数字锁相环平台

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-10-16

一、设计目标

基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。

在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏的估计。

通过USB接口与电脑实现通信来交换有关锁相环的参数。电脑传递锁相环所需的参数(如等效噪声带宽等),FPGA将锁相环的结果传递给电脑(如锁定时间,多普勒频率等)。

二、设计任务

锁相环的输入具有自动增益控制AGC模块,这样可以允许一定动态范围的信号输入,也减少了输入环路信噪比的大幅波动,从而减少了环路噪声带宽的大幅波动。

基于VHDL语言实现数字锁相环,混频基于CORDIC算法,相位提取模块是修正的反正切相位提取,环路滤波器采用理想的二阶环,NCO采用32位的累加器。设计完先进行Modelsim仿真,后利用ISE自带的CHIPSCOPE下载调试。

具有锁定检测模块,当环路锁定时,通过LED灯或数码管给出锁定指示。

通过锁定指示的输出信号,来控制一个实时时钟,这样可以统计锁定时间和失锁时间,所记录的时间存入两个FIFO。

设计USB通信模块,使得设计的锁相环可以同电脑进行通信,将接收电脑传给FPGA的环路参数,同时将检测的锁定时间和失锁时间,锁定指示,多普勒频偏估计等传输给电脑。

利用MATLAB GUI设计一个控制面板,通过控制面板可以随时改变锁相环的环路参数,也可以接收锁相环通过USB传输给电脑的锁相环的结果。

三、设计原理

随着数字技术的发展,现在出现了很多资源丰富的可编程器件,像FPGA、DSP、专用集成电路等,基于软件无线电的通信系统,一般采用数字锁相环。数字锁相环具有锁定精度高,跟踪带宽大,参数可以在不修改硬件电路的前提下进行修改等种种的优点。目前,数字锁相环广泛应用于通信、航天等领域。针对具体的应用,数字锁相环可以用于载波跟踪,相位提取等。本设计就是以载波回复环为依托进行的数字锁相环设计。

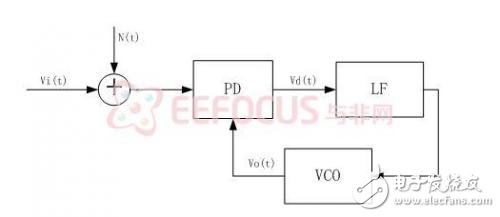

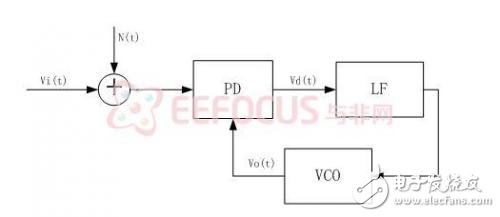

(1)、锁相环的基本框架

锁相环是一个频率与相位的同步控制系统。它的工作过程可用下图表示

图(1)、锁相环基本框图

上面的锁相环是一般模拟锁相环所必需包含的环路组成,包括鉴相器、环路滤波器、压控振荡器。而对于利用软件来实现的全数字锁相环,必须在FPGA内部实现锁相环的鉴相器、环路滤波器、压控振荡器等部件。

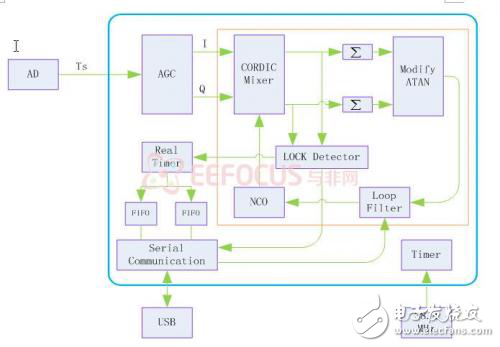

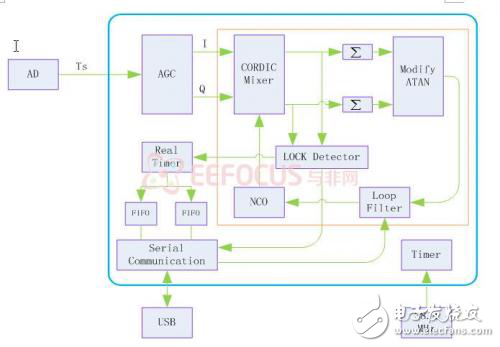

(2)、本设计所要实现的锁相环的基本框架

图(2)、本设计所要实现的锁相环的基本框架

本设计中,鉴相器有CORDIC混频器加上修正的arctan相位提取器组成,环路滤波器有理想二阶环组成,NCO由32位的数字累加器组成。

基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。

在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏的估计。

通过USB接口与电脑实现通信来交换有关锁相环的参数。电脑传递锁相环所需的参数(如等效噪声带宽等),FPGA将锁相环的结果传递给电脑(如锁定时间,多普勒频率等)。

二、设计任务

锁相环的输入具有自动增益控制AGC模块,这样可以允许一定动态范围的信号输入,也减少了输入环路信噪比的大幅波动,从而减少了环路噪声带宽的大幅波动。

基于VHDL语言实现数字锁相环,混频基于CORDIC算法,相位提取模块是修正的反正切相位提取,环路滤波器采用理想的二阶环,NCO采用32位的累加器。设计完先进行Modelsim仿真,后利用ISE自带的CHIPSCOPE下载调试。

具有锁定检测模块,当环路锁定时,通过LED灯或数码管给出锁定指示。

通过锁定指示的输出信号,来控制一个实时时钟,这样可以统计锁定时间和失锁时间,所记录的时间存入两个FIFO。

设计USB通信模块,使得设计的锁相环可以同电脑进行通信,将接收电脑传给FPGA的环路参数,同时将检测的锁定时间和失锁时间,锁定指示,多普勒频偏估计等传输给电脑。

利用MATLAB GUI设计一个控制面板,通过控制面板可以随时改变锁相环的环路参数,也可以接收锁相环通过USB传输给电脑的锁相环的结果。

三、设计原理

随着数字技术的发展,现在出现了很多资源丰富的可编程器件,像FPGA、DSP、专用集成电路等,基于软件无线电的通信系统,一般采用数字锁相环。数字锁相环具有锁定精度高,跟踪带宽大,参数可以在不修改硬件电路的前提下进行修改等种种的优点。目前,数字锁相环广泛应用于通信、航天等领域。针对具体的应用,数字锁相环可以用于载波跟踪,相位提取等。本设计就是以载波回复环为依托进行的数字锁相环设计。

(1)、锁相环的基本框架

锁相环是一个频率与相位的同步控制系统。它的工作过程可用下图表示

图(1)、锁相环基本框图

上面的锁相环是一般模拟锁相环所必需包含的环路组成,包括鉴相器、环路滤波器、压控振荡器。而对于利用软件来实现的全数字锁相环,必须在FPGA内部实现锁相环的鉴相器、环路滤波器、压控振荡器等部件。

(2)、本设计所要实现的锁相环的基本框架

图(2)、本设计所要实现的锁相环的基本框架

本设计中,鉴相器有CORDIC混频器加上修正的arctan相位提取器组成,环路滤波器有理想二阶环组成,NCO由32位的数字累加器组成。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章