资料下载

655MHz低抖动时钟发生器ad9540数据表

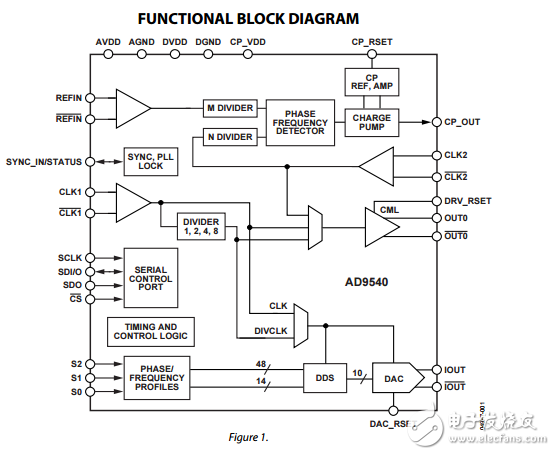

The AD9540 is Analog Devices’ first dedicated clocking product specifically designed to support the extremely stringent clocking requirements of the highest performance data converters. The device features high performance PLL (phaselocked loop) circuitry, including a flexible 200 MHz phase frequency detector and a digitally controlled charge pump current. The device also provides a low jitter, 655 MHz CMLmode, PECL-compliant output driver with programmable slew rates. External VCO rates up to 2.7 GHz are supported. Extremely fine tuning resolution (steps less than 2.33 µHz) is another feature supported by this device. Information is loaded into the AD9540 via a serial I/O port that has a device write speed of 25 Mbps. The AD9540 frequency divider block can also be programmed to support a spread spectrum mode of operation. The AD9540 is specified to operate over the extended automotive range of −40°C to +85°C.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章