资料下载

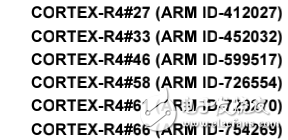

RM42x Microcontroller

The STREXD instruction should work in Thumb mode when Rt and Rt2 are the sameregister.The ARM Architecture permits the Thumb STREXD instruction to be encoded with thesame register used for both transfer registers (Rt and Rt2)。 Because of this erratum, theCortex-R4 processor treats such an encoding as UNPREDICTABLE and executes it as aNOP.This occurs when the processor is in Thumb state and a STREXD instruction isexecuted which has Rt = Rt2. This instruction was new in ARM Architecture version 7(ARMv7)。 It is not present in ARMv6T2 or other earlier architecture versions.If this occurs the destination register, Rd, which indicates the status of the instruction, isnot updated and no memory transaction takes place. If the software is attempting toperform an exclusive read-modify-write sequence, then it might either incorrectlycomplete without memory being written, or loop forever attempting to complete thesequence.This can be avoided by using two different registers for the data to be transferred by aSTREXD instruction. This may involve copying the data in the transfer register to asecond, different register for use by the STREX

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章