资料下载

×

TMS320VC55x系列DSP的Flash烧写方法分析

消耗积分:1 |

格式:rar |

大小:0.6 MB |

2017-10-27

1 引言

随着数字信号处理技术的快速发展,DSP(数字信号处理器)越来越广泛地应用于各种数字信号处理系统中。最终开发的系统要想脱离仿真器运行,必须将程序代码存储在非易失性存储器中。Flash存储器以其大容量和可在线编程等特点已成为DSP系统的一个基本配置。如何将程序烧写进Flash,并在上电时加载到DSP内部的RAM是Flash在DSP系统中应用的两个基本技术问题。本文以基于TI公司的TMS320VC5509A和Atmel公司的AT49LV1024 Flash开发的系统为背景,详细介绍了系统引导相关的硬件设计、烧写软件设计以及自举引导和二次引导等实现方法。

2 TMS320VC5509A的自举引导

2.1 TMS320VC5509A的自举模式配置

TMS320VC5509A每次上电复位后,在执行完一系列初始化(配置堆栈寄存器、关闭中断、程序临时入口、符号扩展、兼容性配置)工作后,根据预先配置的自举模式,通过固化在ROM内的Bootloader程序进行程序引导。VC5509A的引导模式选择是通过4个模式选择引脚BOOTM[0:3]配置完成的。 BOOTM0~3引脚分别与GPIO1、2、3、0相连。在本系统设计中,采用EMIF(外部存储接口)并行引导模式(16位数据宽度),只需将BOOTM[3:0]设置成1011即可。

EMIF为外部存储接口,通过EMIF接口可以灵活地和各种同步或异步存储器件无缝连接。通过EMIF可以将VC5509A的存储空间扩展到128 Mbit(SDRAM),存储空间共被分为CE0~CE3四个段,每段占用不同的地址。在EMIF的并行引导模式中,ROM固化的Bootloader程序是以0x200000为首地址开始加载程序。0x200000即为CE1空间的首地址,所以Flash必须接在DSP的CE1空间上。在加载时。EMIF的CE1空间已经默认配置成异步静态随机存储器(SRAM)接口,并且在时序上采用了最差情况设置(即最慢访问速度),充分保证了时间裕量,使得程序代码顺利地加载到DSP的内存中。

2.2 TMS320VC5509A的引导表

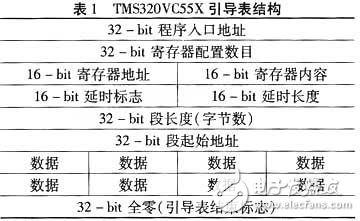

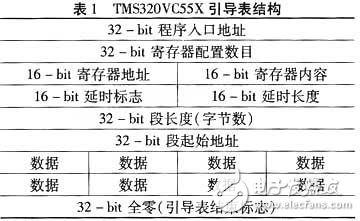

Bootloader在引导程序时,程序代码是以引导表格形式加载的。TMS320VC55x的引导表结构中包括了用户程序的代码段和数据段以及相应段在内存中的指定存储位置,此外还包括了程序人口地址、部分寄存器的配置值、可编程延时时间等信息。TMS320VC55x系列DSP的引导表结构如表1所示。

其中,程序入口地址是引导表加载结束后,用户程序开始执行的地址;寄存器配置数目决定了后面有多少个寄存器需要配置;只有当延时标志为0xFFFF时,延时才被执行;延时长度决定了在寄存器配置后延时多少个CPU周期才进行下一个动作;段长度、段起始地址和数据则为用户程序中定义的各个段的内容,并且可以重复添加;最后以0x00000000(32个0)作为引导表的结束标志。

随着数字信号处理技术的快速发展,DSP(数字信号处理器)越来越广泛地应用于各种数字信号处理系统中。最终开发的系统要想脱离仿真器运行,必须将程序代码存储在非易失性存储器中。Flash存储器以其大容量和可在线编程等特点已成为DSP系统的一个基本配置。如何将程序烧写进Flash,并在上电时加载到DSP内部的RAM是Flash在DSP系统中应用的两个基本技术问题。本文以基于TI公司的TMS320VC5509A和Atmel公司的AT49LV1024 Flash开发的系统为背景,详细介绍了系统引导相关的硬件设计、烧写软件设计以及自举引导和二次引导等实现方法。

2 TMS320VC5509A的自举引导

2.1 TMS320VC5509A的自举模式配置

TMS320VC5509A每次上电复位后,在执行完一系列初始化(配置堆栈寄存器、关闭中断、程序临时入口、符号扩展、兼容性配置)工作后,根据预先配置的自举模式,通过固化在ROM内的Bootloader程序进行程序引导。VC5509A的引导模式选择是通过4个模式选择引脚BOOTM[0:3]配置完成的。 BOOTM0~3引脚分别与GPIO1、2、3、0相连。在本系统设计中,采用EMIF(外部存储接口)并行引导模式(16位数据宽度),只需将BOOTM[3:0]设置成1011即可。

EMIF为外部存储接口,通过EMIF接口可以灵活地和各种同步或异步存储器件无缝连接。通过EMIF可以将VC5509A的存储空间扩展到128 Mbit(SDRAM),存储空间共被分为CE0~CE3四个段,每段占用不同的地址。在EMIF的并行引导模式中,ROM固化的Bootloader程序是以0x200000为首地址开始加载程序。0x200000即为CE1空间的首地址,所以Flash必须接在DSP的CE1空间上。在加载时。EMIF的CE1空间已经默认配置成异步静态随机存储器(SRAM)接口,并且在时序上采用了最差情况设置(即最慢访问速度),充分保证了时间裕量,使得程序代码顺利地加载到DSP的内存中。

2.2 TMS320VC5509A的引导表

Bootloader在引导程序时,程序代码是以引导表格形式加载的。TMS320VC55x的引导表结构中包括了用户程序的代码段和数据段以及相应段在内存中的指定存储位置,此外还包括了程序人口地址、部分寄存器的配置值、可编程延时时间等信息。TMS320VC55x系列DSP的引导表结构如表1所示。

其中,程序入口地址是引导表加载结束后,用户程序开始执行的地址;寄存器配置数目决定了后面有多少个寄存器需要配置;只有当延时标志为0xFFFF时,延时才被执行;延时长度决定了在寄存器配置后延时多少个CPU周期才进行下一个动作;段长度、段起始地址和数据则为用户程序中定义的各个段的内容,并且可以重复添加;最后以0x00000000(32个0)作为引导表的结束标志。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章