资料下载

×

TMS320C55x DSP并行处理技术分析

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-11-03

TMS320C55x DSP是一种高性能的数字信号处理器,其强大的并行处理能力能够进一步提高其运算能力。本文介绍了C55xDSP的内核结构以及用户自定义并行指令时必须遵守如下3条并行处理基本规则,并介绍了6种典型的并行处理应用。利用本文介绍的方法使用并行处理能力将有效提高程序执行效率,同时降低系统功耗。

德州仪器公司(TI)的TMS320C55x(简称C55x)DSP内核是在TMS320C54x(简称C54x)基础上开发出来的,并可以兼容C54x的源代码。C55x的内核电压降到了1V,功耗降到0.05mW/MIPS,是C54x的1/6。C55x的运行时钟可以达到 200MHz,是C54x的两倍,再加上C55x在C54x结构上作了相当大的扩展,程序执行时可以大量采用并行处理,这样使得C55x的实际运算能力可以达到300MIPS以上。

C55x DSP已越来越多地应用于各种手持便携终端当中。以下我们将通过详细介绍C55x的CPU内核结构,讨论其并行处理技术的应用。

C55x DSP内核结构

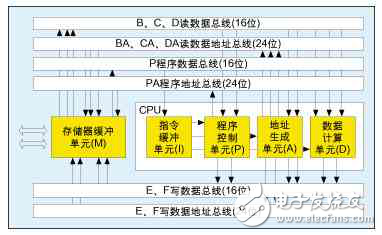

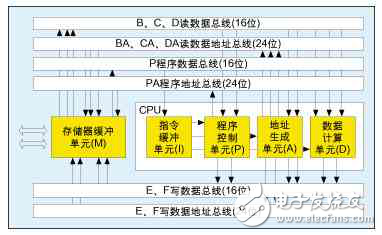

C55x DSP是一款采用改良型哈佛结构,高度模块化的数字信号处理器拥有比普通DSP更为丰富的硬件资源,能够有效提高运算能力。其内核结构如图1所示。

图1

整个处理器内部分为5个大的功能单元:存储器缓冲单元(M单元)、指令缓冲单元(I单元)、程序控制单元(P单元)、地址生成单元(A单元)和数据计算单元(D 单元),各个功能单元之间通过总线连接。C55x DSP中有1条32位程序数据总线(P总线),1条24位程序地址总线(PA总线),5条16位的数据总线(B、C、D、E、F总线)和5条24位的数据地址总线(BA、CA、DA、EA、FA总线)。这种高度模块化的多总线结构使得C55x DSP拥有超强的并行处理能力。[next]

M单元主要管理数据区(包括I/O数据区)与中央处理器(CPU)之间的数据传送,使得高速CPU与外部相对低速的存储器之间在吞吐量上的瓶颈可以得到一定程度的缓解。

I单元从程序数据总线接收程序代码,并将其放入指令缓冲队列(IBQ)中,然后利用指令译码器将指令缓冲队列中的程序代码进行译码,最后再将译码后的指令送给P单元、A单元、D单元进行处理。

德州仪器公司(TI)的TMS320C55x(简称C55x)DSP内核是在TMS320C54x(简称C54x)基础上开发出来的,并可以兼容C54x的源代码。C55x的内核电压降到了1V,功耗降到0.05mW/MIPS,是C54x的1/6。C55x的运行时钟可以达到 200MHz,是C54x的两倍,再加上C55x在C54x结构上作了相当大的扩展,程序执行时可以大量采用并行处理,这样使得C55x的实际运算能力可以达到300MIPS以上。

C55x DSP已越来越多地应用于各种手持便携终端当中。以下我们将通过详细介绍C55x的CPU内核结构,讨论其并行处理技术的应用。

C55x DSP内核结构

C55x DSP是一款采用改良型哈佛结构,高度模块化的数字信号处理器拥有比普通DSP更为丰富的硬件资源,能够有效提高运算能力。其内核结构如图1所示。

图1

整个处理器内部分为5个大的功能单元:存储器缓冲单元(M单元)、指令缓冲单元(I单元)、程序控制单元(P单元)、地址生成单元(A单元)和数据计算单元(D 单元),各个功能单元之间通过总线连接。C55x DSP中有1条32位程序数据总线(P总线),1条24位程序地址总线(PA总线),5条16位的数据总线(B、C、D、E、F总线)和5条24位的数据地址总线(BA、CA、DA、EA、FA总线)。这种高度模块化的多总线结构使得C55x DSP拥有超强的并行处理能力。[next]

M单元主要管理数据区(包括I/O数据区)与中央处理器(CPU)之间的数据传送,使得高速CPU与外部相对低速的存储器之间在吞吐量上的瓶颈可以得到一定程度的缓解。

I单元从程序数据总线接收程序代码,并将其放入指令缓冲队列(IBQ)中,然后利用指令译码器将指令缓冲队列中的程序代码进行译码,最后再将译码后的指令送给P单元、A单元、D单元进行处理。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章