资料下载

×

如何使用实现FPGA的RMII通讯模块的设计

消耗积分:0 |

格式:rar |

大小:0.31 MB |

2018-10-18

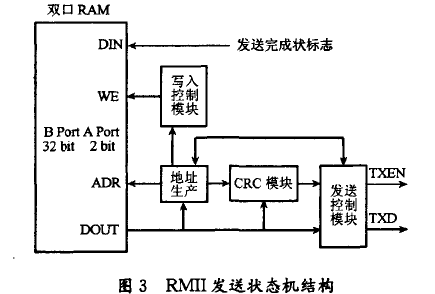

某鱼雷声自导的硬件系统使用了百兆网络交换机实现DSP之间的互联。交换机在MAC和PHY之间的接I=I是RMII,但DSP没有相应的外围设备与它匹配。因此必须在FPGA中设计RMII的通讯模块,完成DSP数据格式向RMII数据格式的转化。在设计中将该通讯模块分为发送状态机和接收状态机两部分。每个状态机均包含2个2 kbyte的双口RAM作为乒乓缓冲。双121 RAM的一端位宽2 bit作为RMII的数据端口,另一端位宽32 bit作为DSP数据端口。向该端口的指定地址写命令字能够启动数据发送,向指定地址读状态字能够判断是否有数据接收。该通讯模块工作在全双工模式,文中给出了它的一个应用实例。经测试它能够达到收发11 M byte/s以上的速度,并且占用的F王)GA硬件资源较少,满足了系统网络通讯的要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章