资料下载

STM32F4xxxx系列ARM内核的32位微控制器的参考手册免费下载

本参考手册面向应用开发人员,提供有关使用 STM32F405xx/07xx、STM32F415xx/17xx、 STM32F42xxx 和 STM32F43xxx 微控制器存储器与外设的完整信息。

STM32F405xx/07xx、STM32F415xx/17xx、STM32F42xxx 和 STM32F43xxx 构成一个微 控制器系列,各产品具有不同的存储器大小、封装和外设。

本节简要介绍本文档中所用首字母缩略词和缩写词的定义:

● 在本文档中,将具有 FPU 的 Cortex-M4 内核称为 Cortex-M4F

● CPU 内核集成了两个调试端口:

— JTAG 调试端口 (JTAG-DP) 提供基于联合测试工作组 (JTAG) 协议的 5 引脚标准接口。

— SWD 调试端口 (SWD-DP) 提供基于串行线调试 (SWD) 协议的 2 引脚(时钟和数据)接口。

有关 JTAG 和 SWD 协议的信息,请参见《Cortex-M4F 技术参考手册》。

● 字:32 位数据/指令。

● 半字:16 位数据/指令。

● 字节:8 位数据。

● 双字:64 位数据。

● IAP(在应用中编程):IAP 是指可以在用户程序运行期间对微控制器的 Flash 进行重新编程。

● ICP(在线编程):ICP 是指可以在器件安装于用户应用电路板上时使用 JTAG 协议、SWD 协议或自举程序对微控制器的 Flash 进行编程。

● I-Code:此总线用于将 CPU 内核的指令总线连接到 Flash 指令接口。通过此总线可执行预取操作。

● D-Code:此总线用于将 CPU 的 D-Code 总线(数据加载和调试访问)连接到 Flash 数据接口。

● 选项字节:存储于 Flash 中的产品配置位。

● OBL:选项字节加载器。

● AHB:高级高性能总线。

● CPU:指 Cortex-M4F 内核。

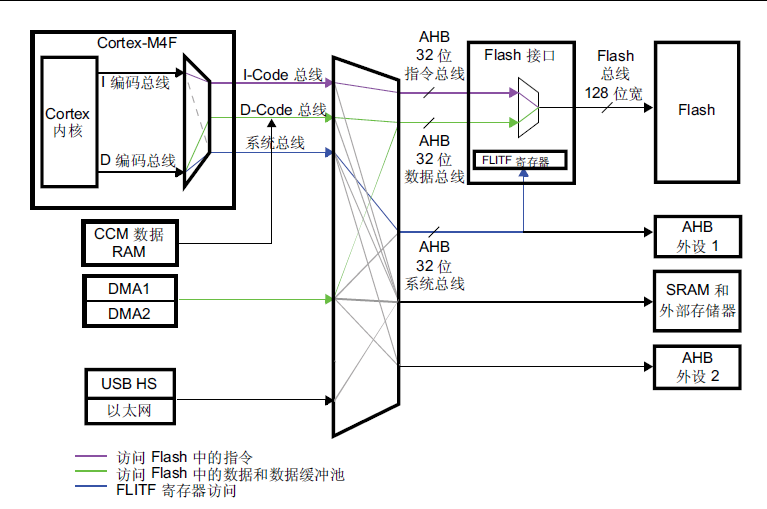

系统架构

主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连:

● 八条主控总线:

— Cortex™-M4F 内核 I 总线、D 总线和 S 总线

— DMA1 存储器总线

— DMA2 存储器总线

— DMA2 外设总线

— 以太网 DMA 总线

— USB OTG HS DMA 总线

● 七条被控总线:

— 内部 Flash ICode 总线

— 内部 Flash DCode 总线

— 主要内部 SRAM1 (112 KB)

— 辅助内部 SRAM2 (16 KB)

— 辅助内部 SRAM3 (64 KB)(仅适用于 STM32F42xxx 和 STM32F43xxx 器件)

— AHB1 外设(包括 AHB-APB 总线桥和 APB 外设)

— AHB2 外设

— FSMC

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章